# 2020 Wilson Research Group Functional Verification Study

Harry Foster

October 2020

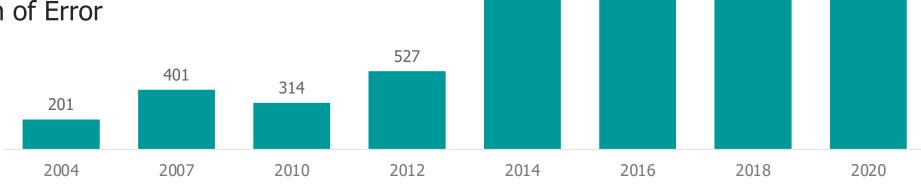

## **2020 Study Background**

Our worldwide study is highly respected and referenced

- Study pool not based on Mentor's customer list

- Double blind study

- Sample frame for 2020: **1492** participants

- 7.4x larger than 2004 Ron Collett International study

- Confidence interval 95%

- ±3% Margin of Error

1886

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

1738

1492

1205

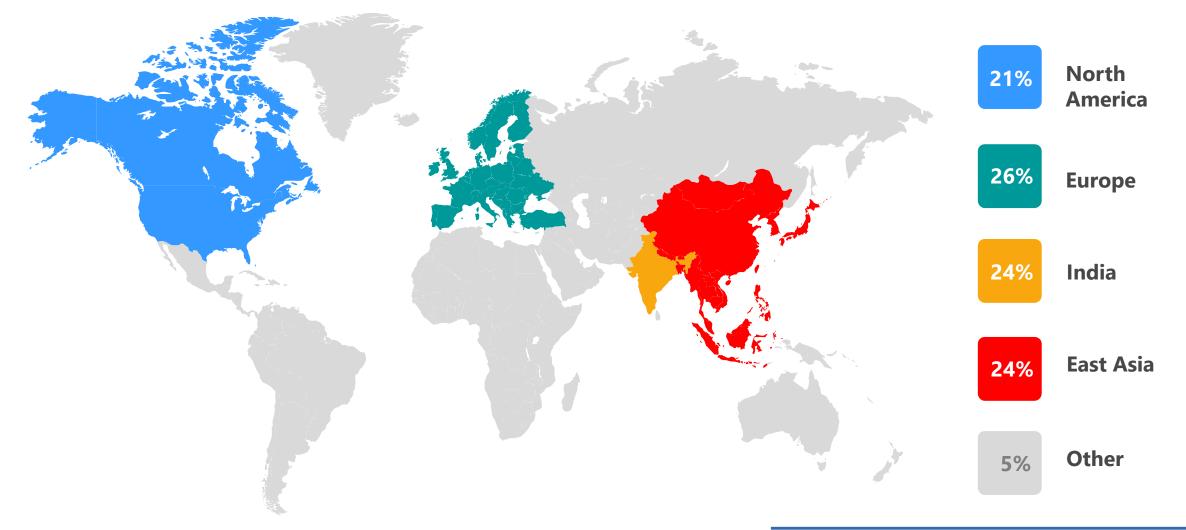

### **2020 Study Demographics**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

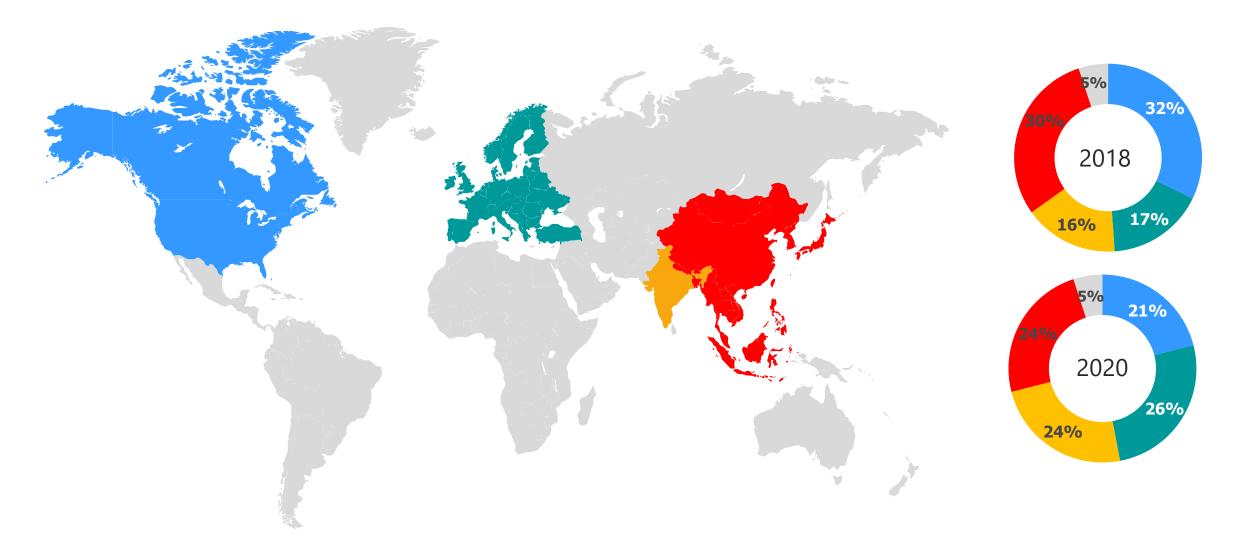

#### 2018 vs 2020 Study Demographics

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

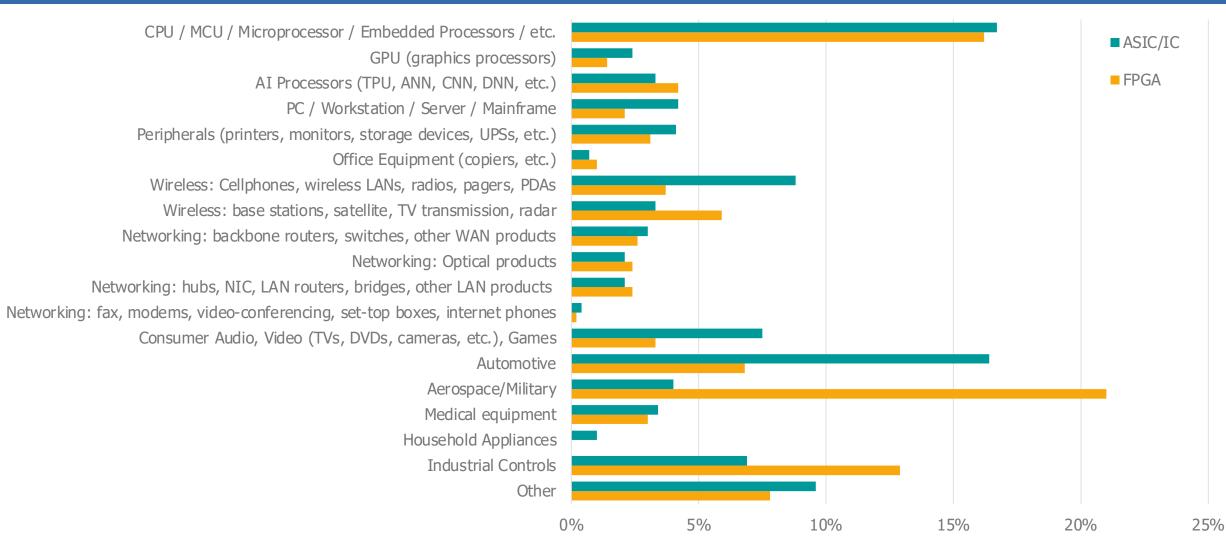

## **2020 Study Participation by Market Segment**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

© 2020 Mentor Graphics Corporation

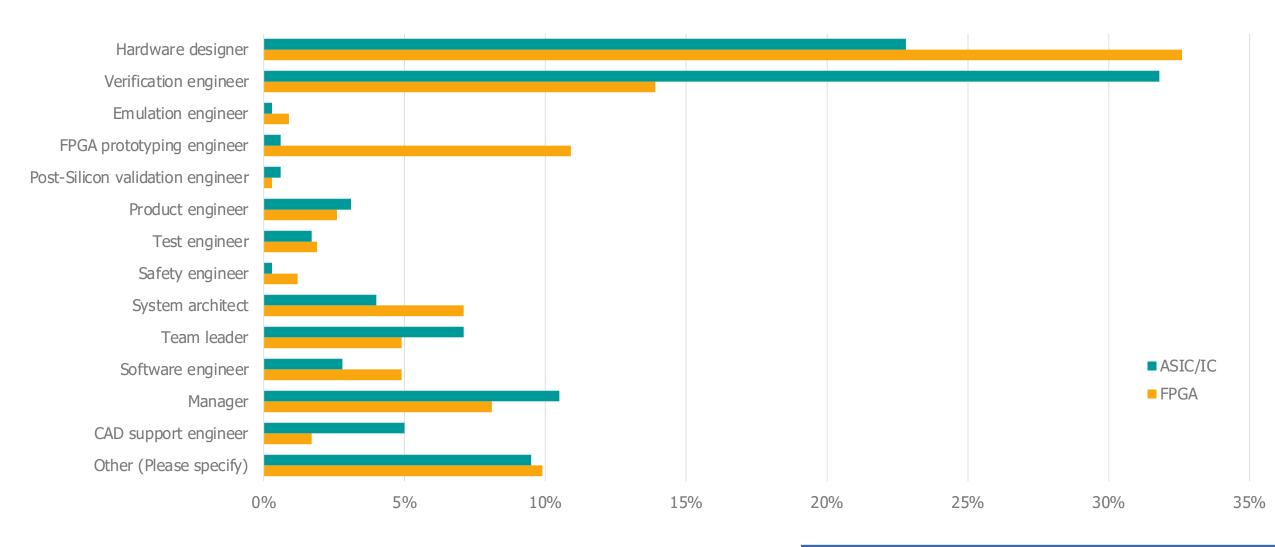

## **2020 Study Participation by Job Title**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

© 2020 Mentor Graphics Corporation

# **PARTICIPANT'S CURRENT DESIGN**

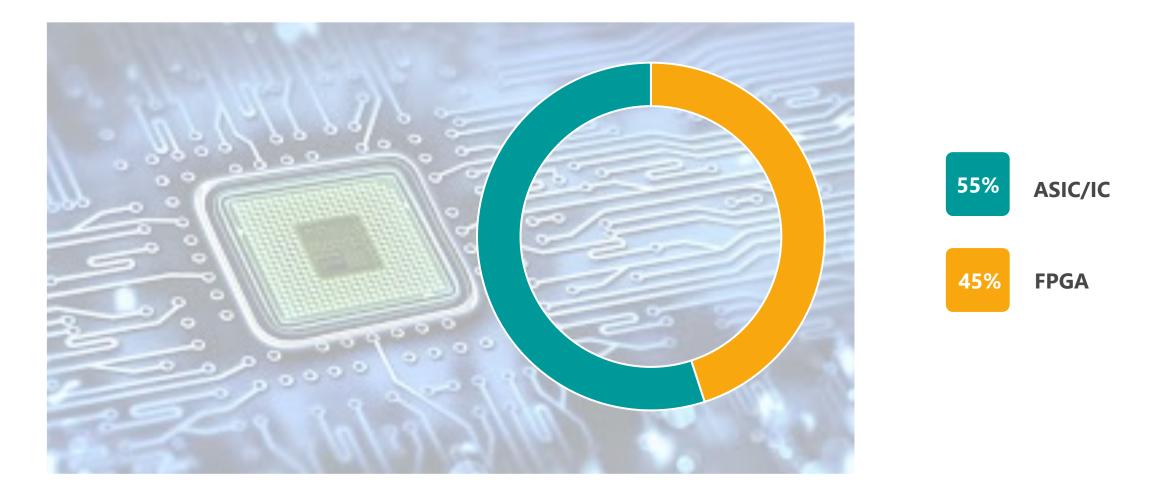

#### **2020 Study Participation by Targeted Implementation**

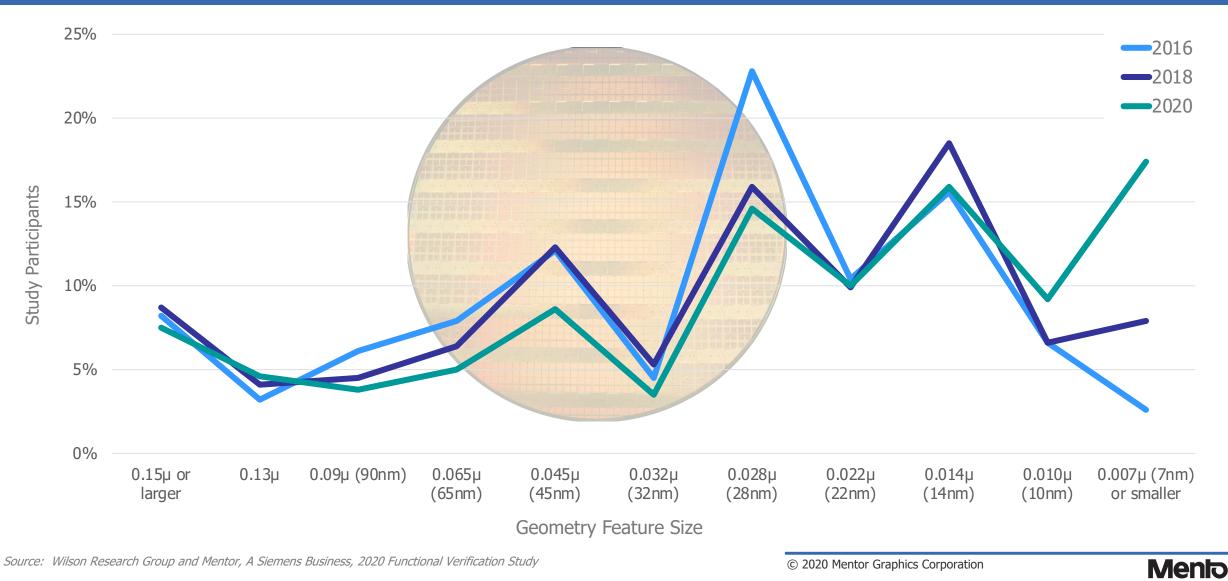

### **Study Participation by Geometry Feature Size**

A Siemens Busines

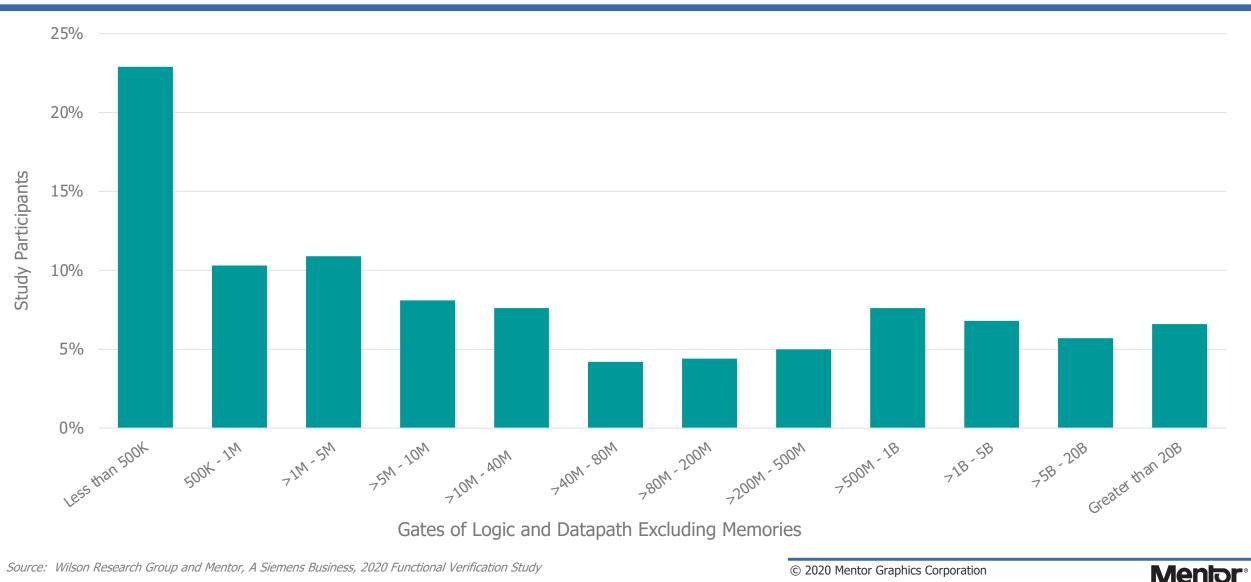

#### **2020 ASIC Study Participation by Gate Count**

Siemens Busines

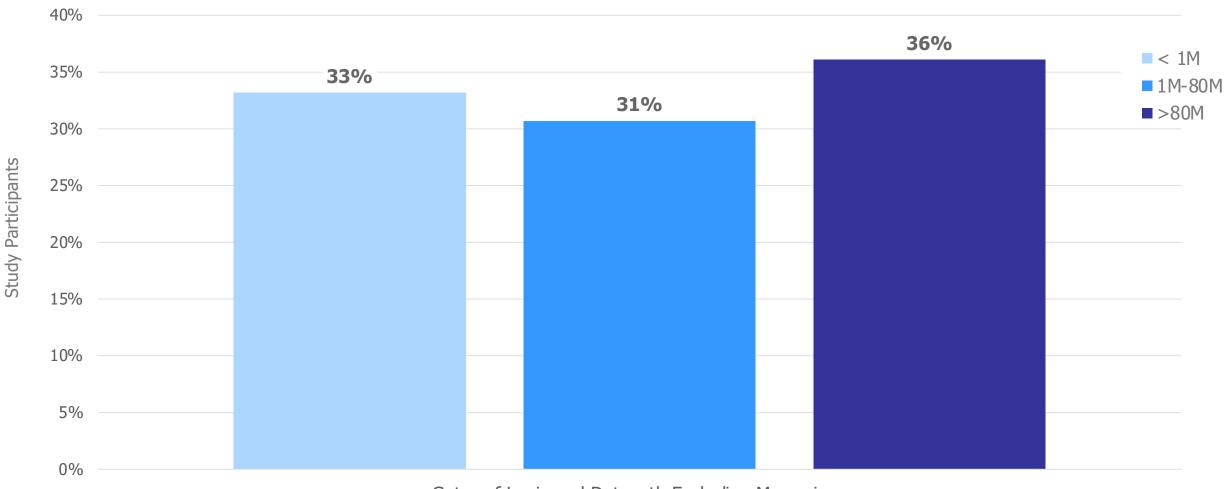

#### **2020 ASIC Study Participants by Design Size**

Gates of Logic and Datapath Excluding Memories

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

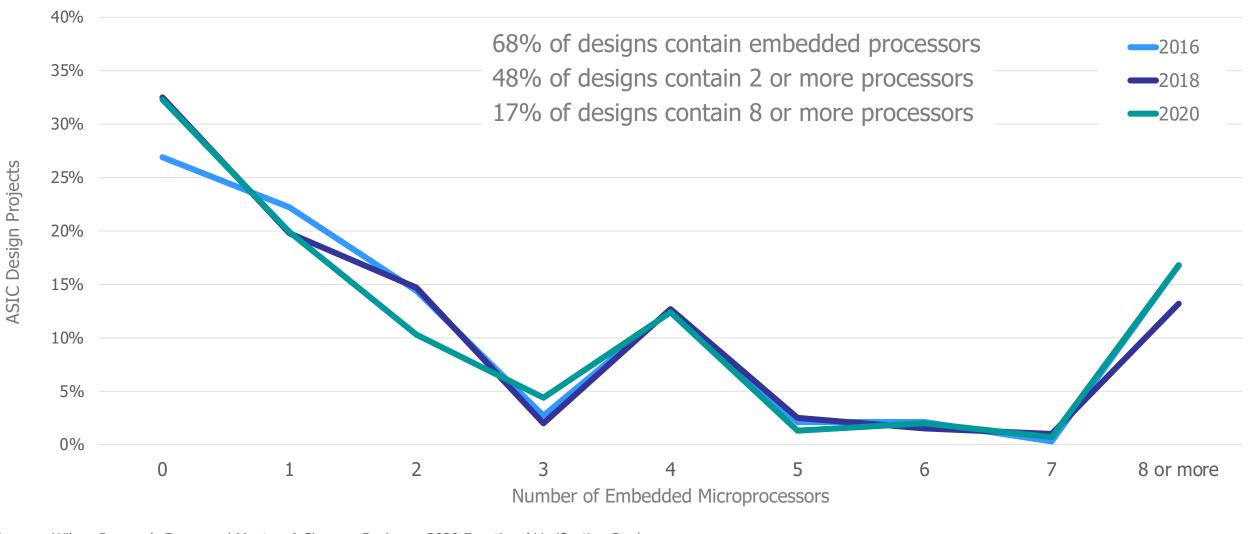

#### **ASIC Number of Embedded Microprocessors**

© 2020 Mentor Graphics Corporation

Men

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

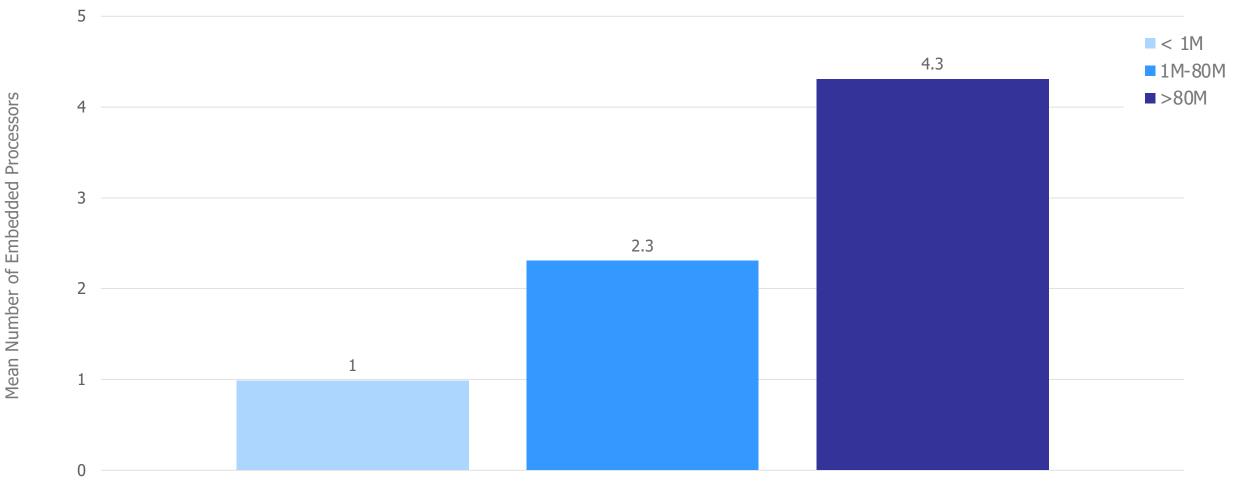

#### **ASIC Mean Number of Embedded Microprocessors by Design Size**

**ASIC:** Mean Number of Embedded Microprocessors by Design Size

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

© 2020 Mentor Graphics Corporation

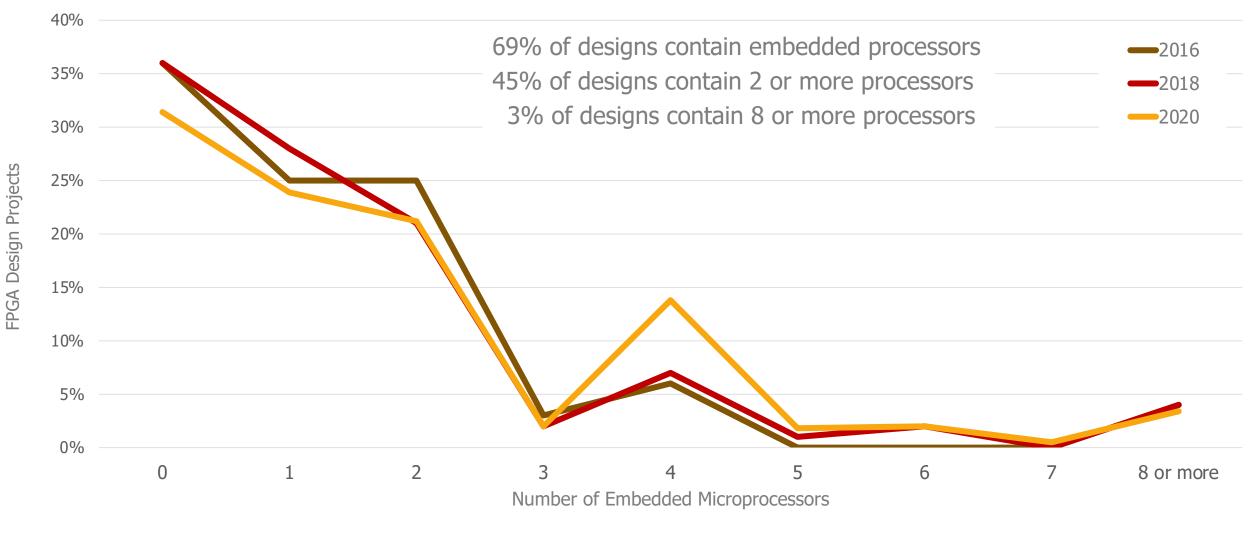

#### **FPGA Number of Embedded Microprocessors**

© 2020 Mentor Graphics Corporation

Men

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

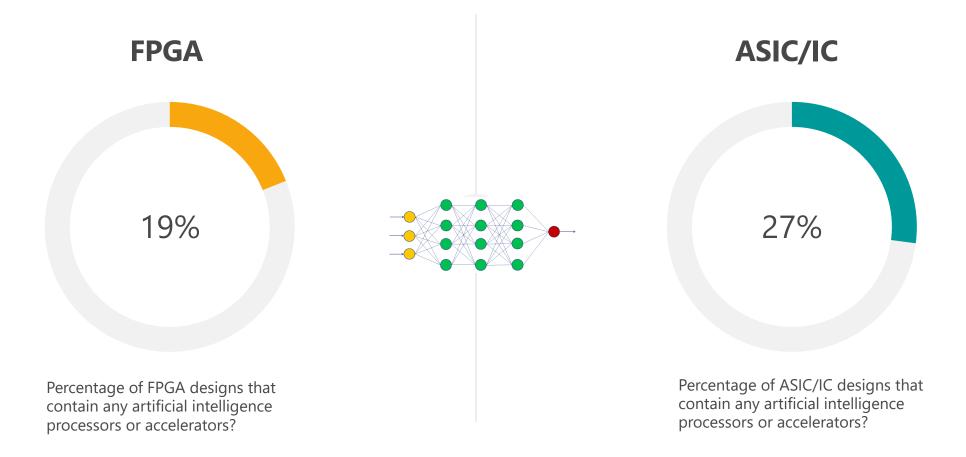

#### **Projects Incorporating AI Processors/Accelerators**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

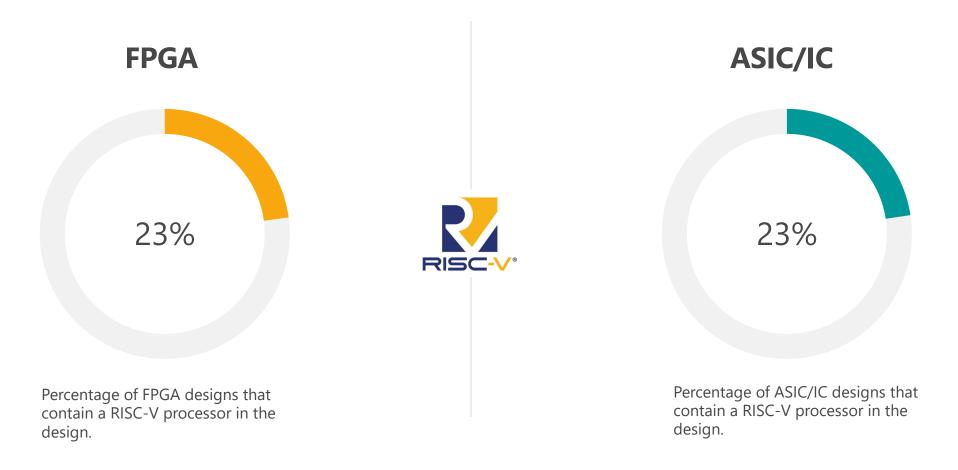

#### **Projects Incorporating RISC-V Processors in Design**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

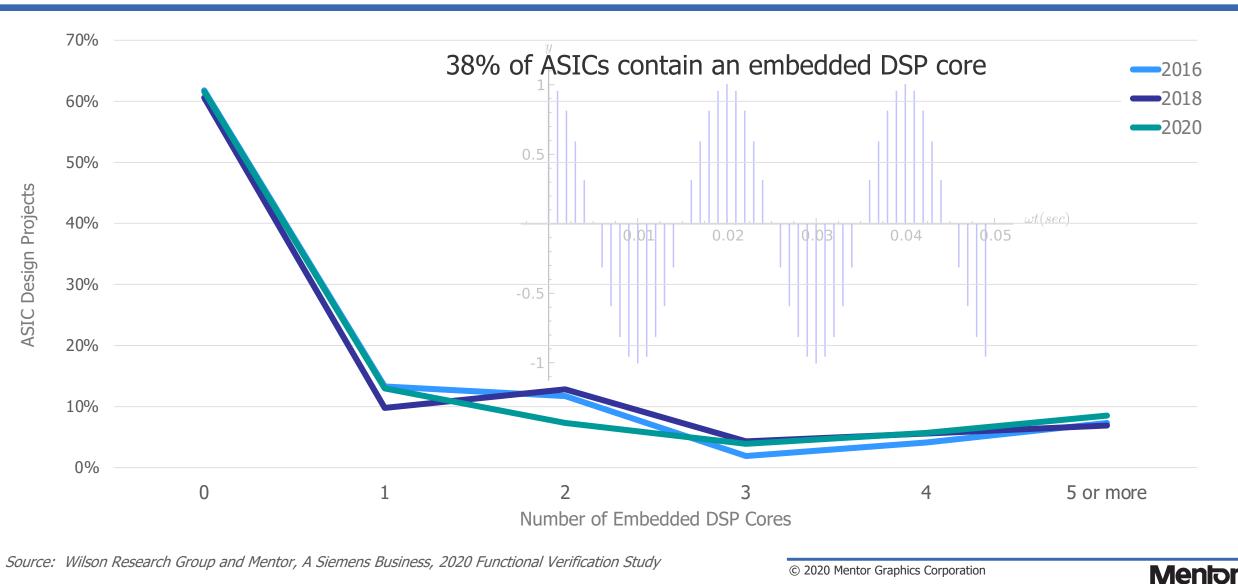

#### **ASIC Number of Embedded DSP Cores**

Siemens Busines

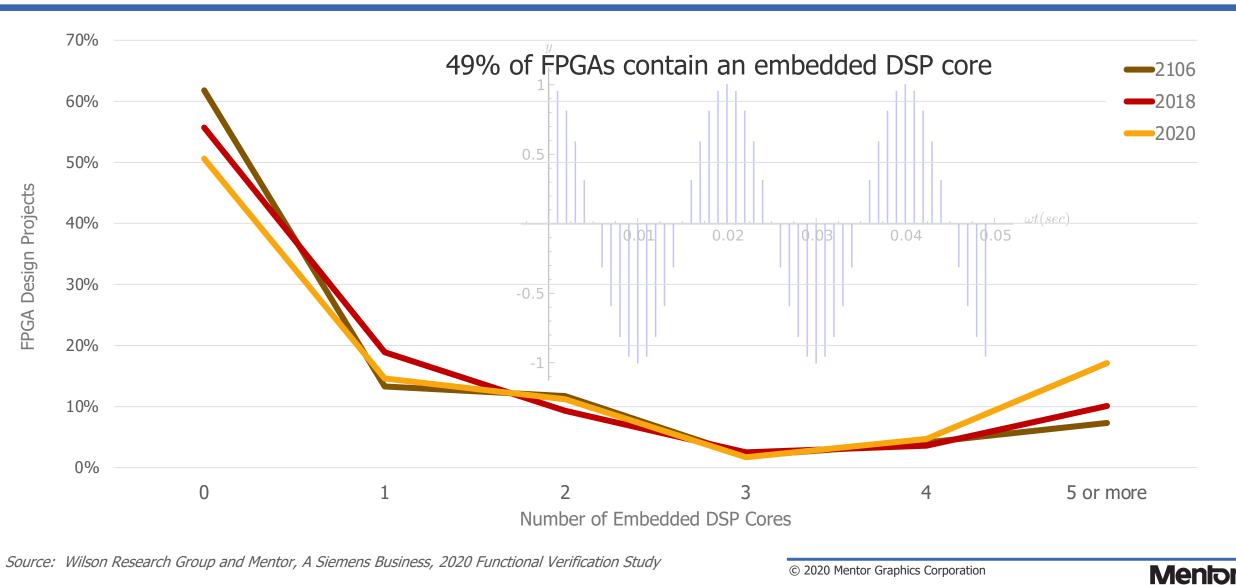

#### **FPGA Number of Embedded DSP Cores**

Siemens Busines

#### **Design Projects Implementing Security Features**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

#### **Projects Working on Safety Critical Design**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

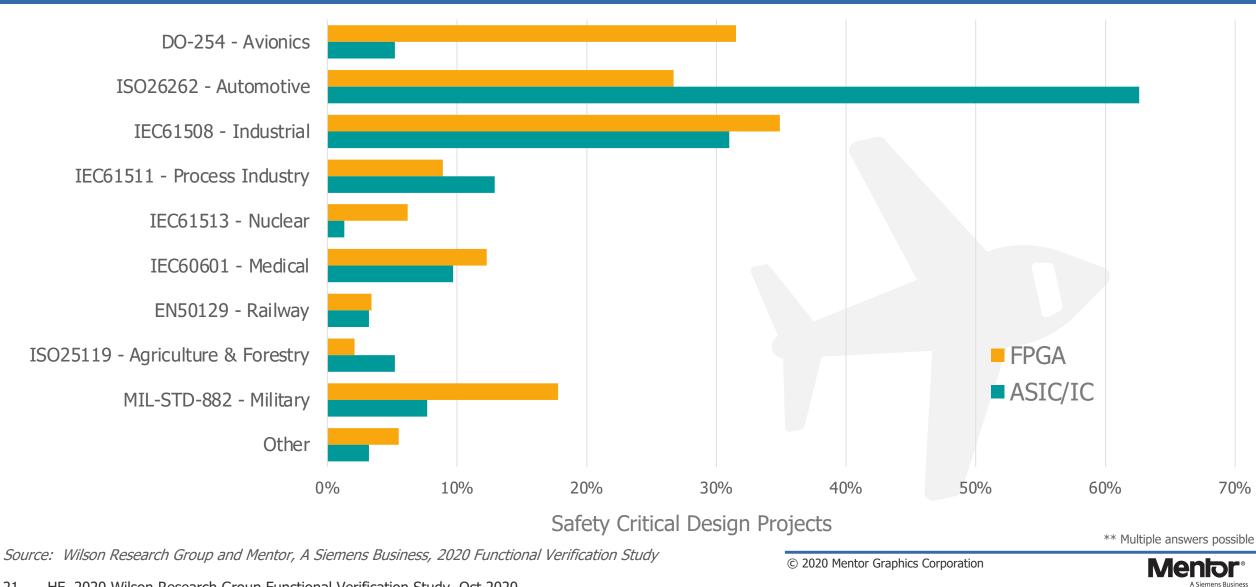

#### **Adoption of Various Functional Safety Standards**

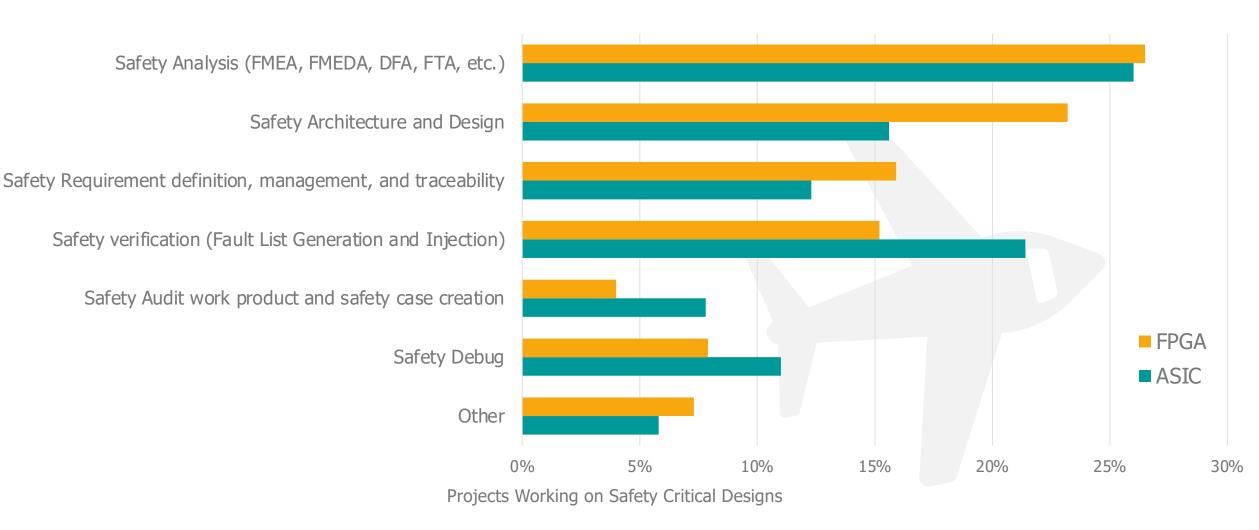

#### **Biggest Functional Safety Project Challenge**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

22 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

© 2020 Mentor Graphics Corporation

# **PROJECT RESOURCES**

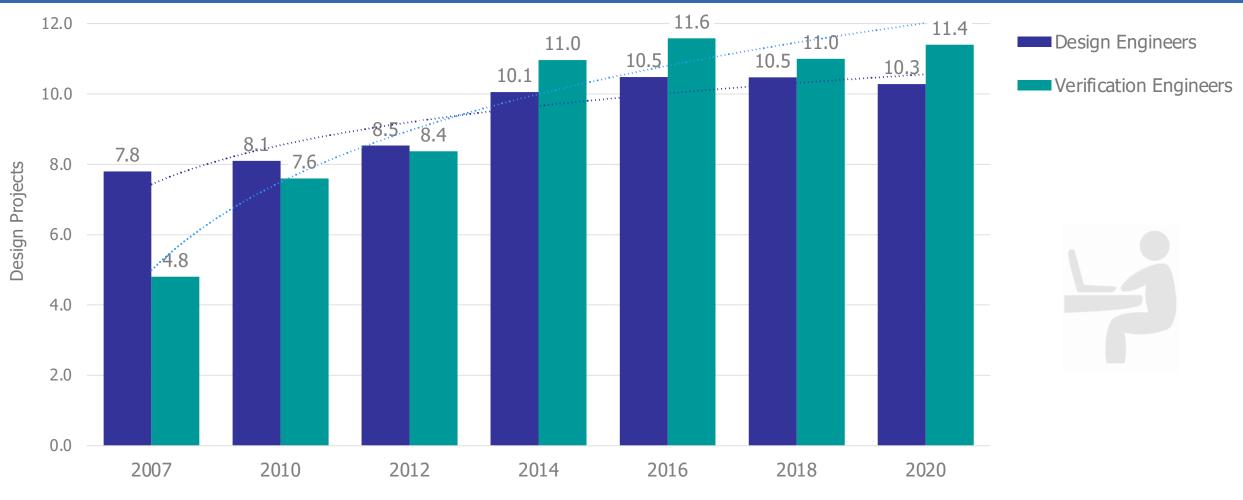

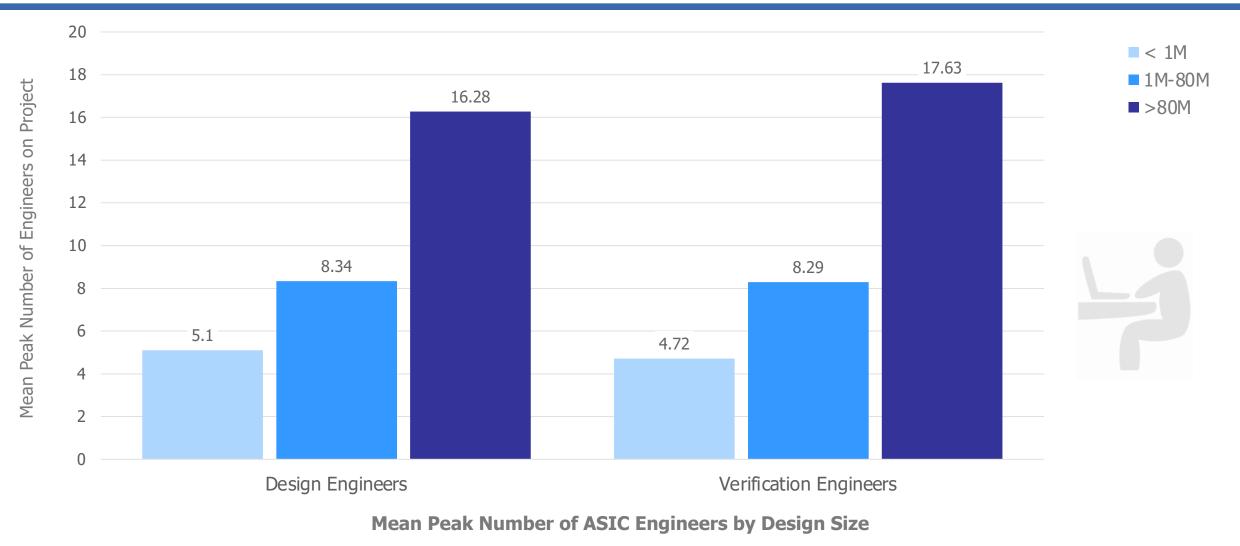

#### Mean Peak Number of Engineers on an ASIC/IC Project

Mean Peak Number of Engineers on ASIC/IC Projects

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

#### Mean Peak Number of Engineers By ASIC/IC Design Size

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

© 2020 Mentor Graphics Corporation

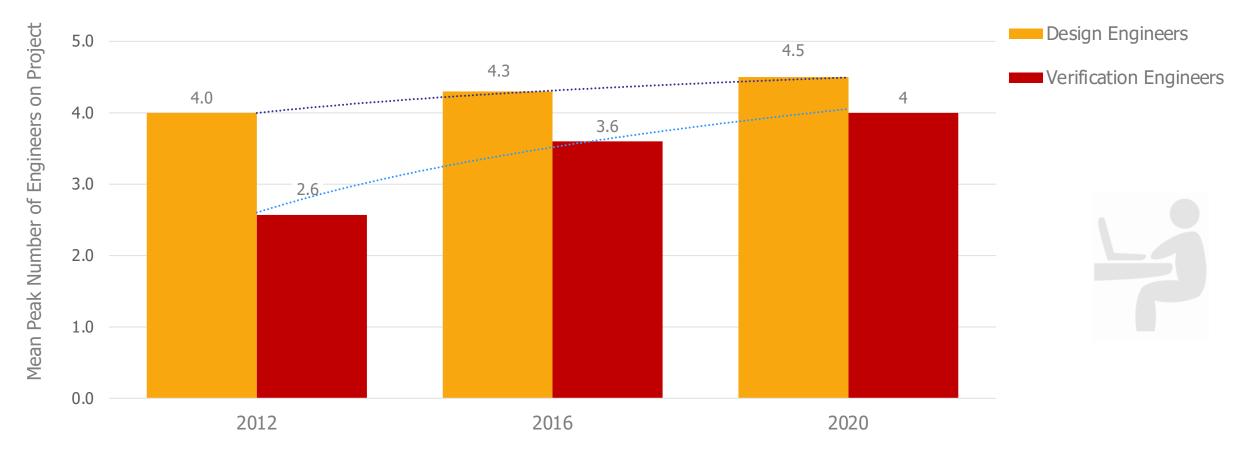

#### **Mean Peak Number of Engineers on a FPGA Project**

Mean Peak Number of Engineers on FPGA Project

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

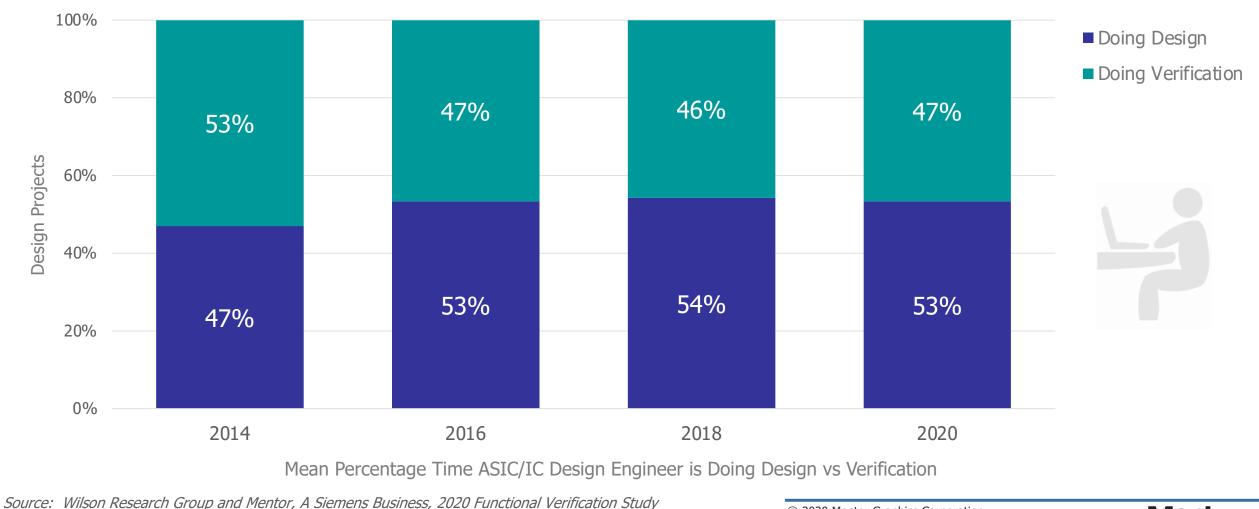

#### Mean Time ASIC/IC Design Engineer is Doing Design vs Verification

27 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

© 2020 Mentor Graphics Corporation

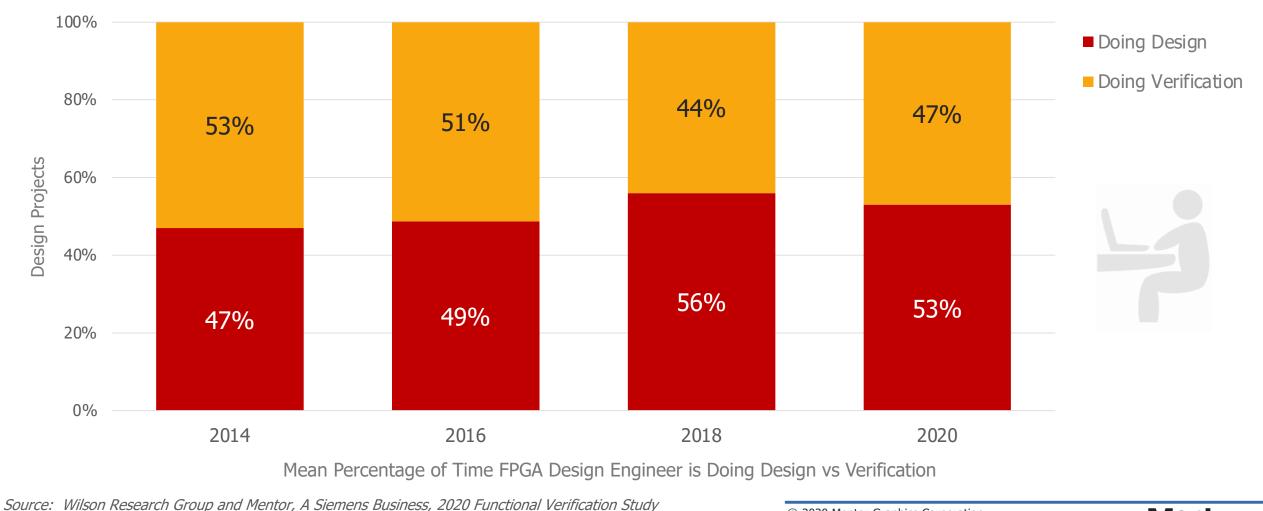

#### Mean Time Design FPGA Engineer is Doing Design vs Verification

28 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

© 2020 Mentor Graphics Corporation

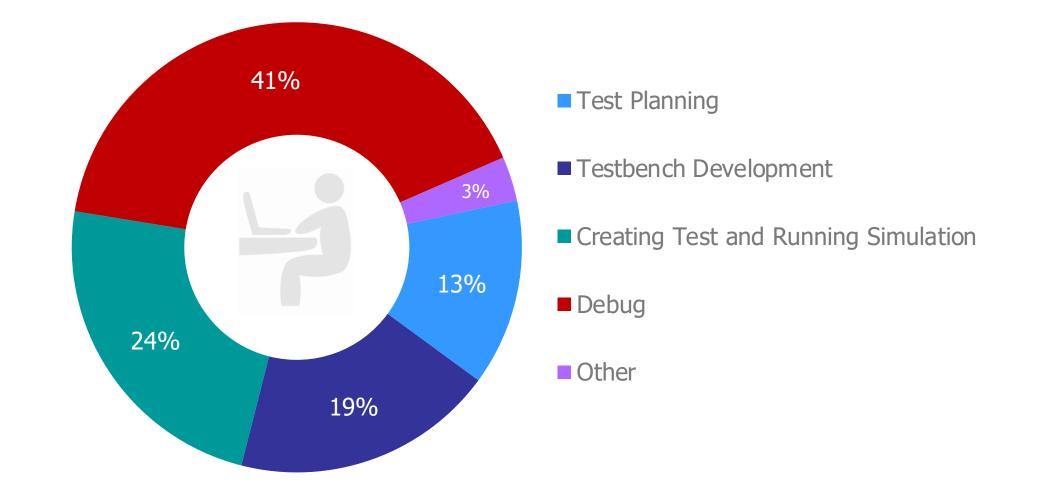

#### Where ASIC/IC Verification Engineers Spend Their Time

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

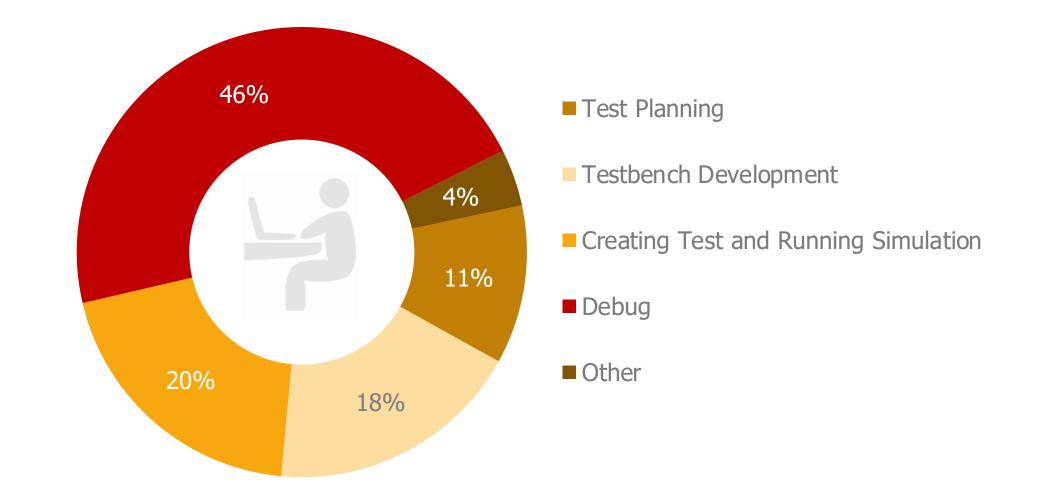

#### **Where FPGA Verification Engineers Spend Their Time**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

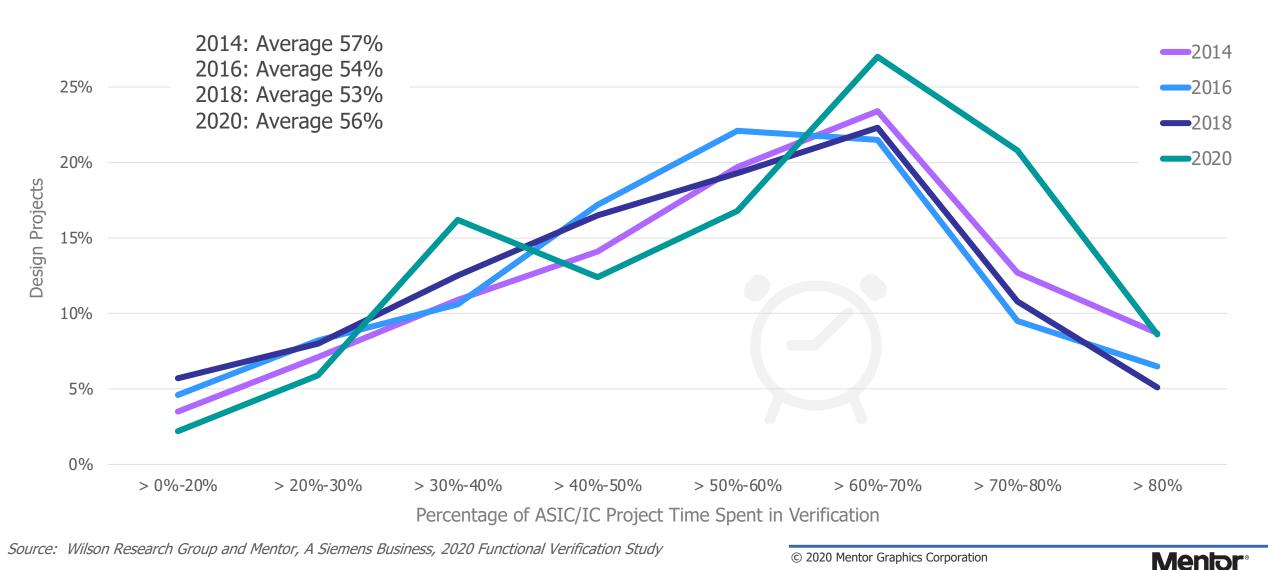

#### Percentage of ASIC/IC Project Time Spent in Verification

Siemens Busines

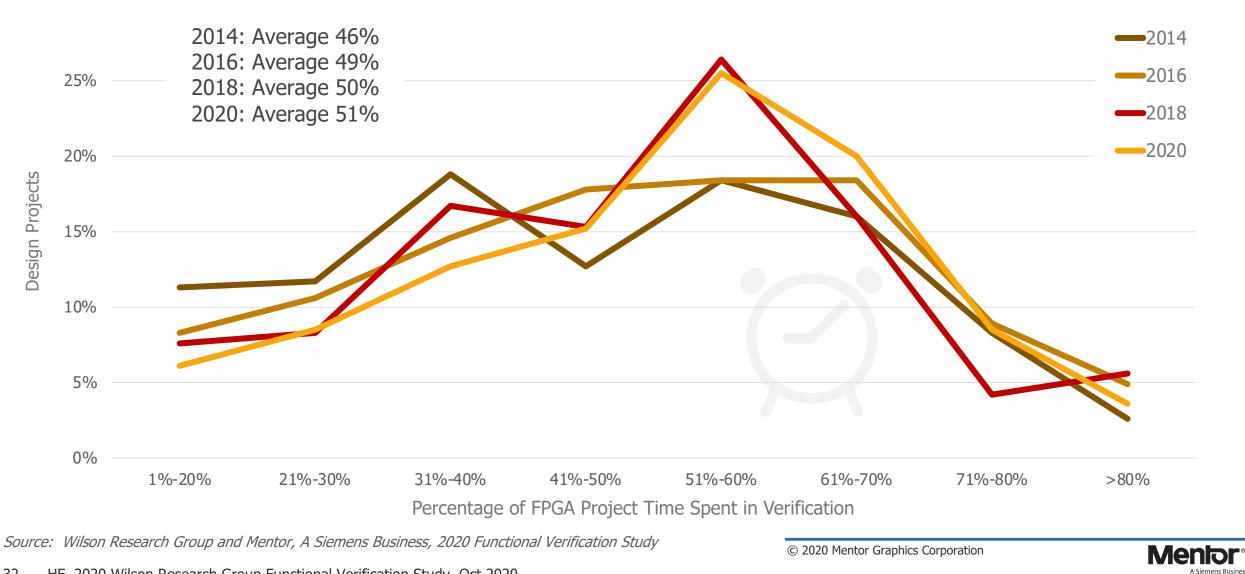

#### **Percentage of FPGA Project Time Spent in Verification**

# **VERIFICATION RESULTS**

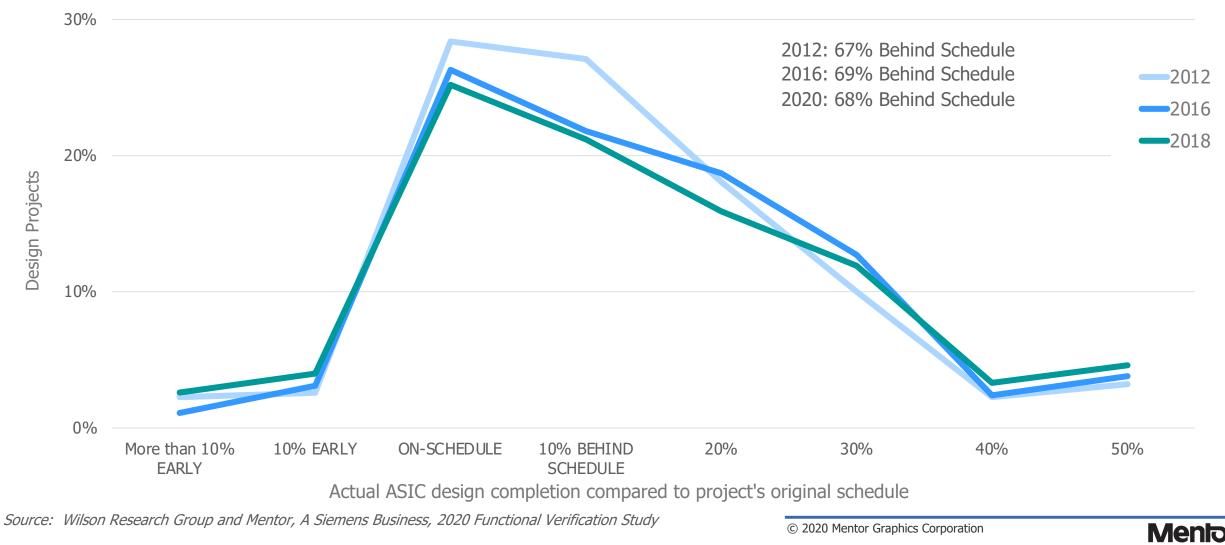

#### **ASIC Completion to Project's Original Schedule**

Siemens Busines

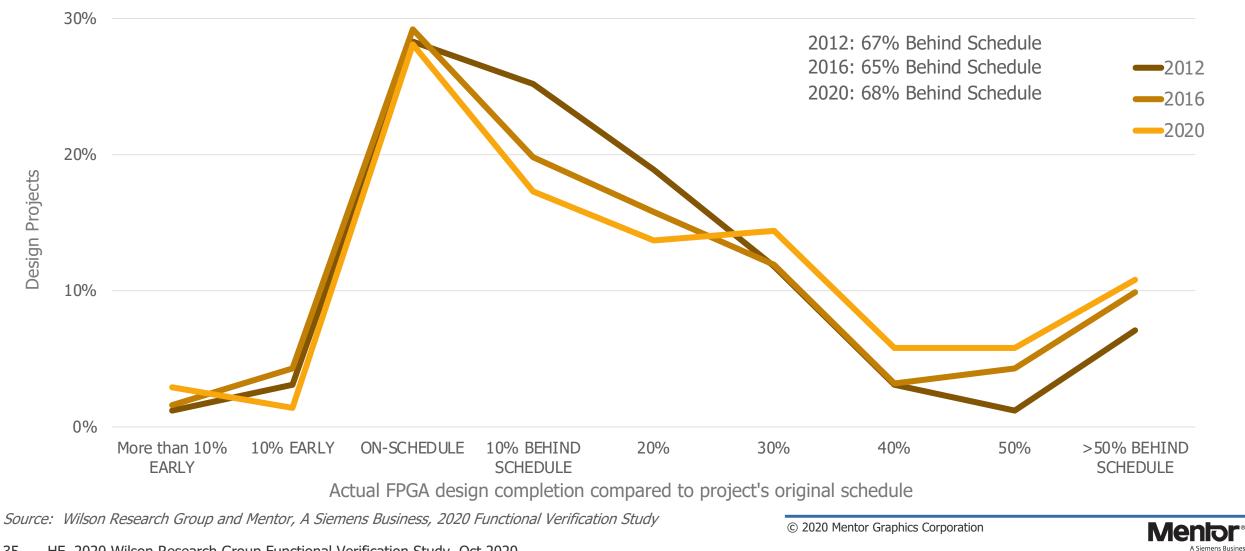

#### **FPGA Completion to Project's Original Schedule**

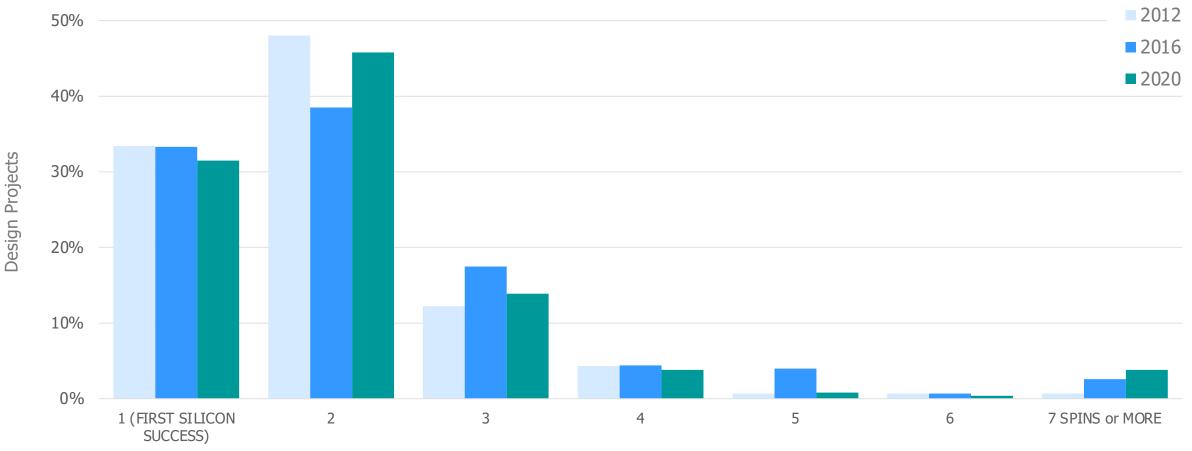

#### **ASIC Number of Required Spins Before Production**

**Number of Required ASIC Spins Before Production**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

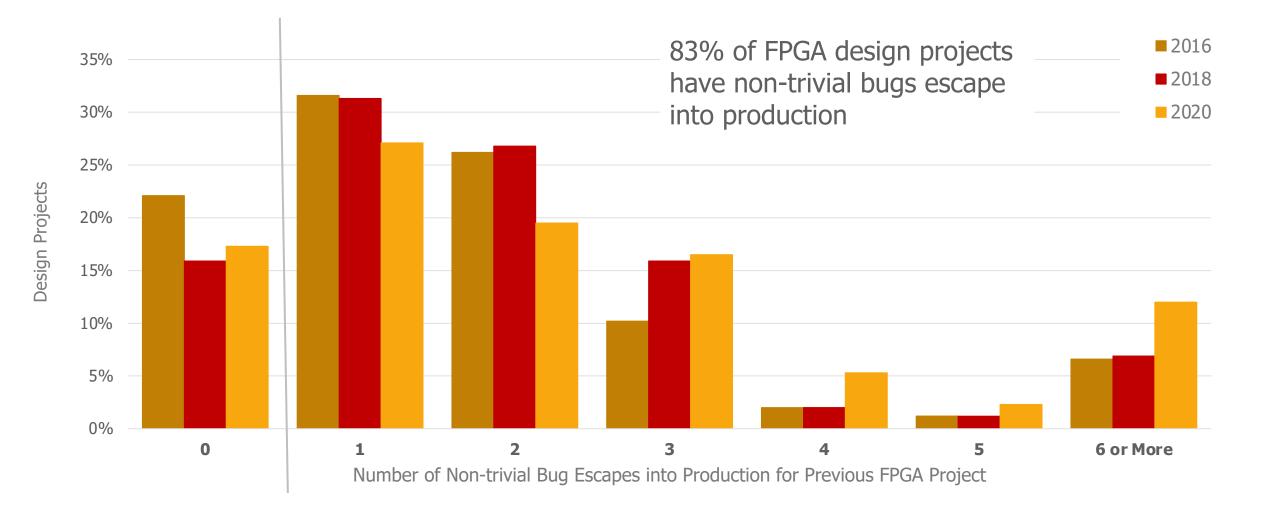

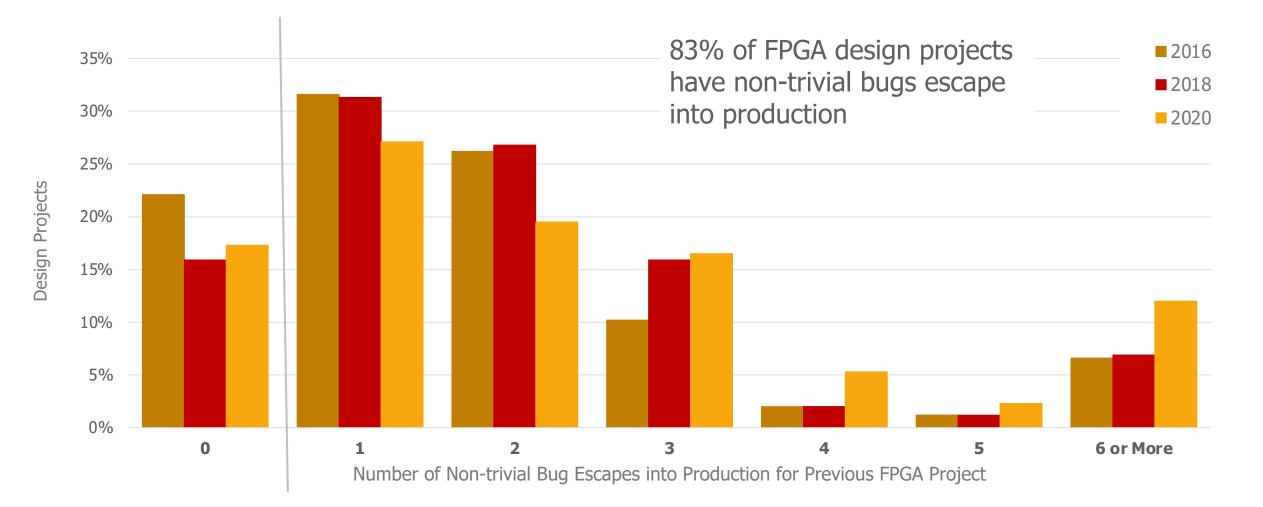

#### **Number of Non-trivial FPGA Bug Escapes into Production**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

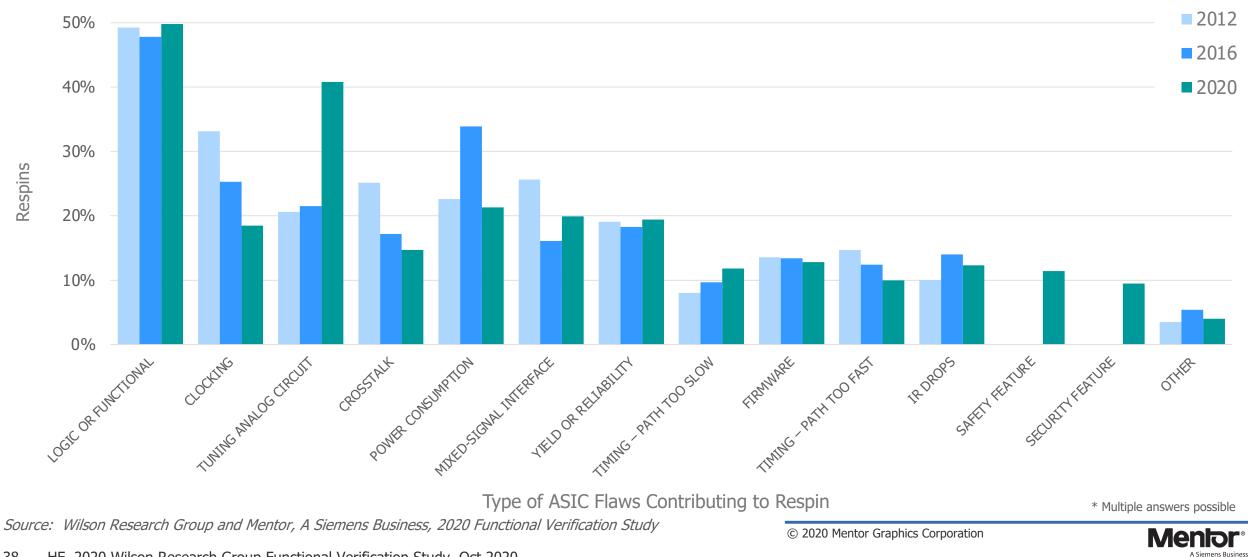

## **ASIC Type of Flaws Contributing to Respin**

<sup>38</sup> HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

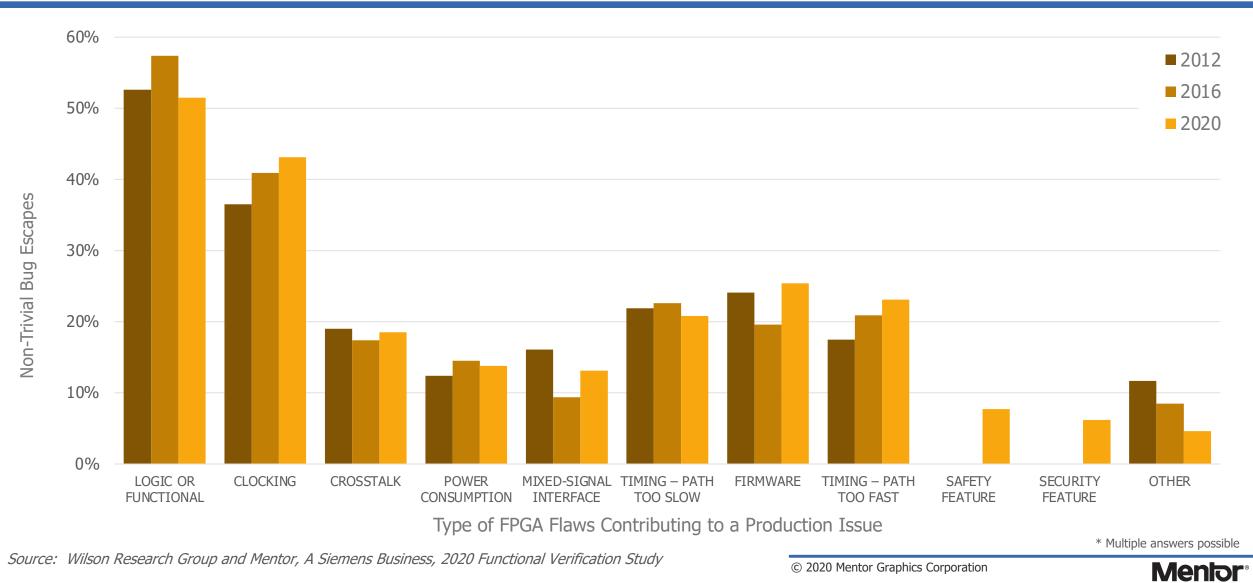

## **FPGA Type of Flaws Contributing to a Production Issue**

A Siemens Business

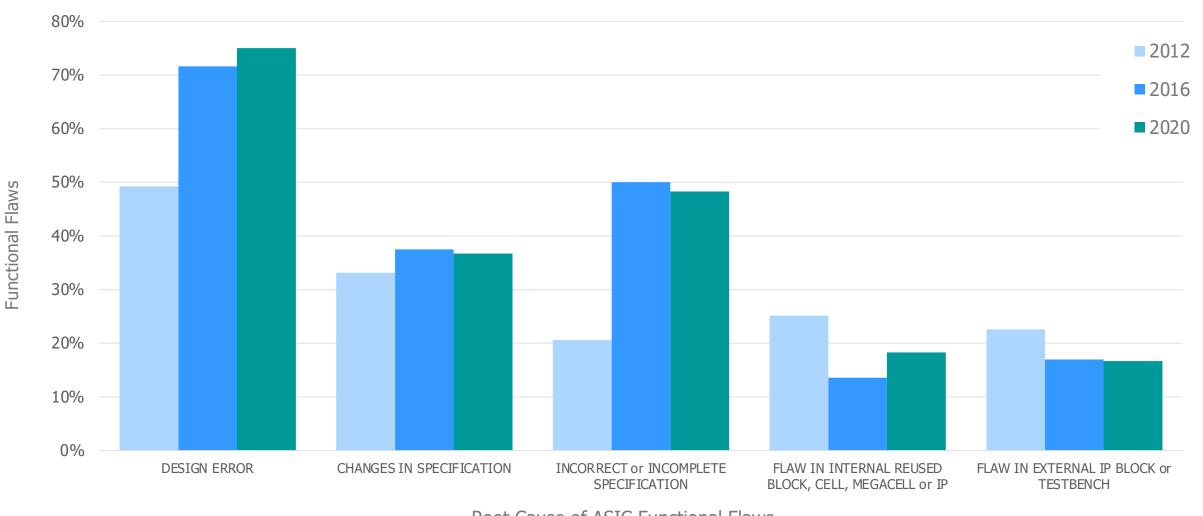

#### **Root Cause of ASIC Functional Flaws**

Root Cause of ASIC Functional Flaws

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

40

\* Multiple answers possible

HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

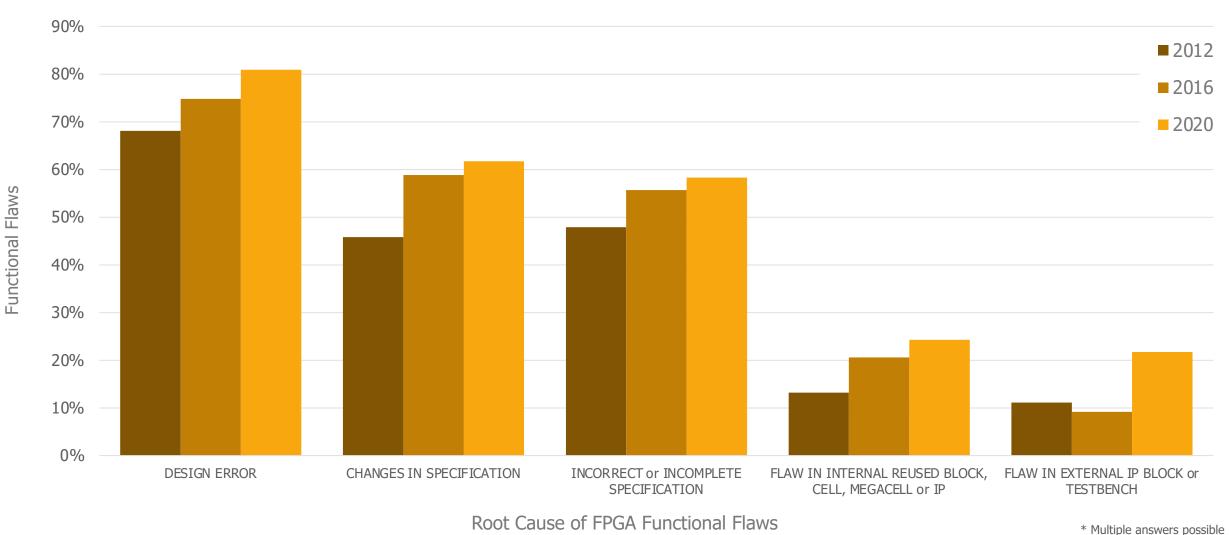

#### **Root Cause of FPGA Functional Flaws**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

41 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

# LANGUAGES & METHODOLOGIES

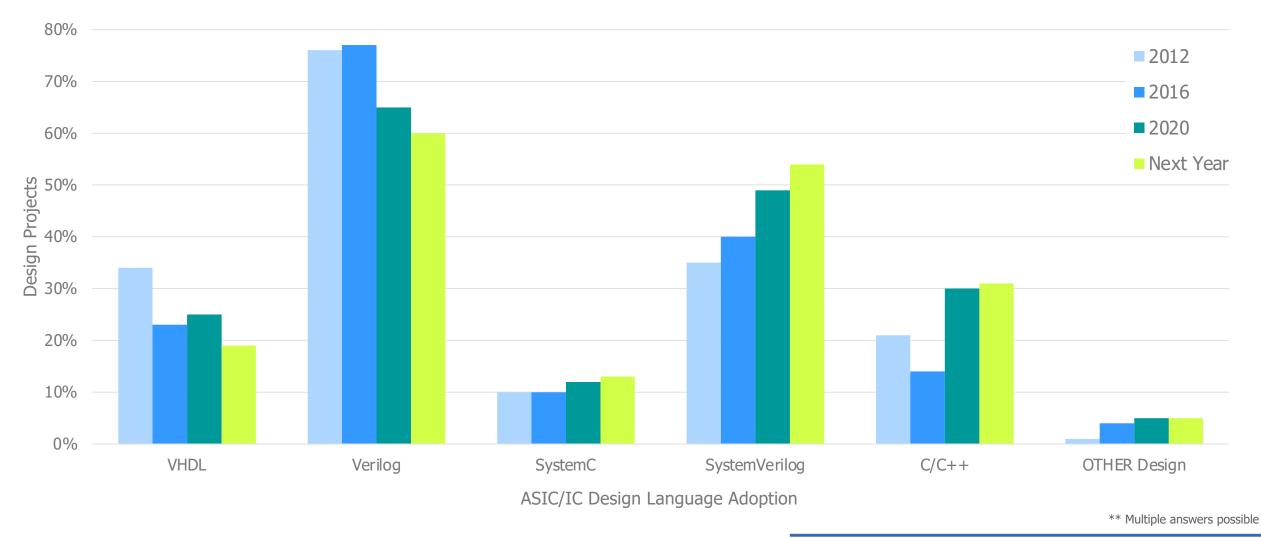

#### **ASIC/IC Design Language Adoption Next Twelve Months**

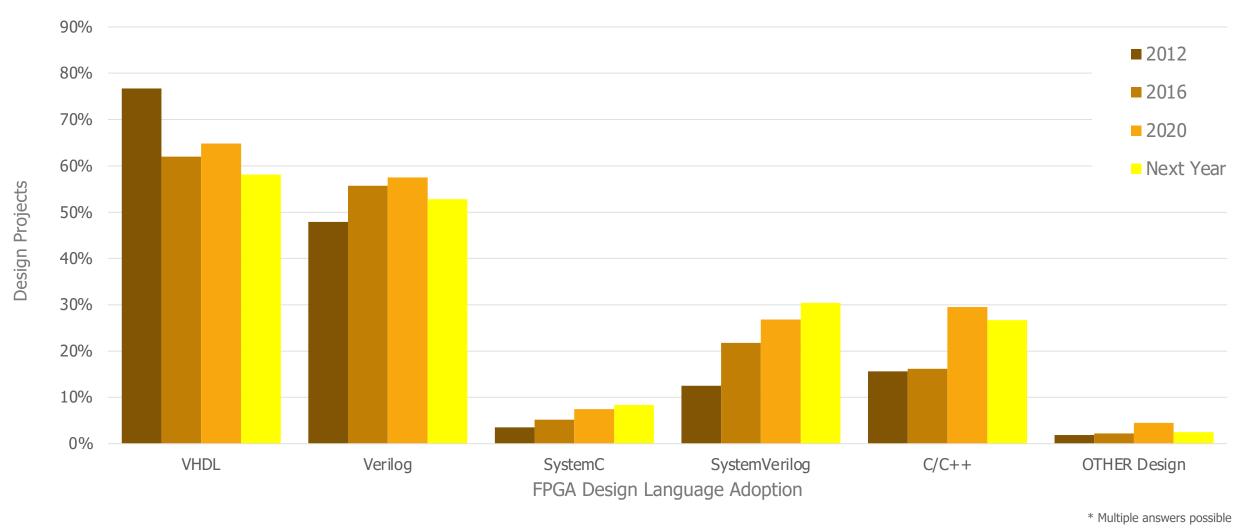

#### **FPGA Design Language Adoption Next Twelve Months**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

44 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

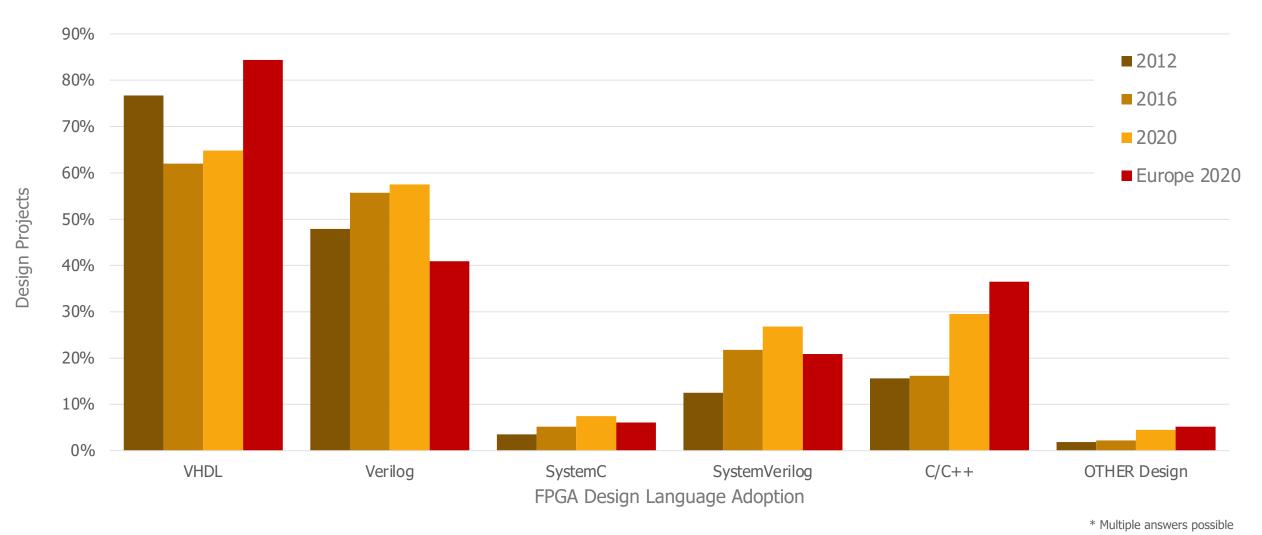

#### **FPGA Design Language Adoption in Europe**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

45 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

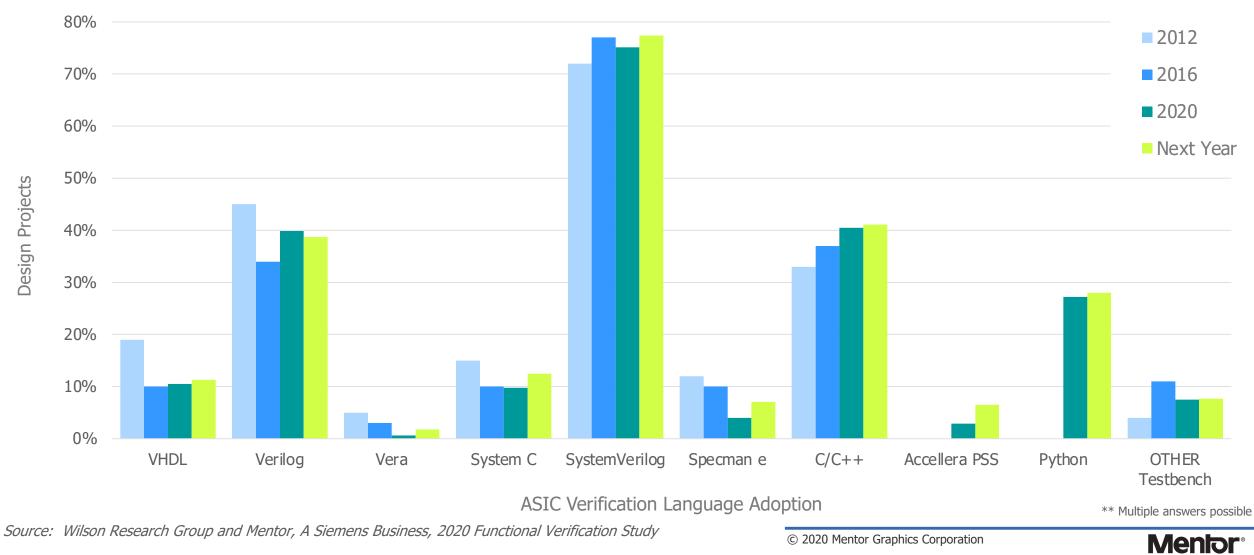

#### **ASIC/IC Verification Language Adoption Next Twelve Months**

A Siemens Business

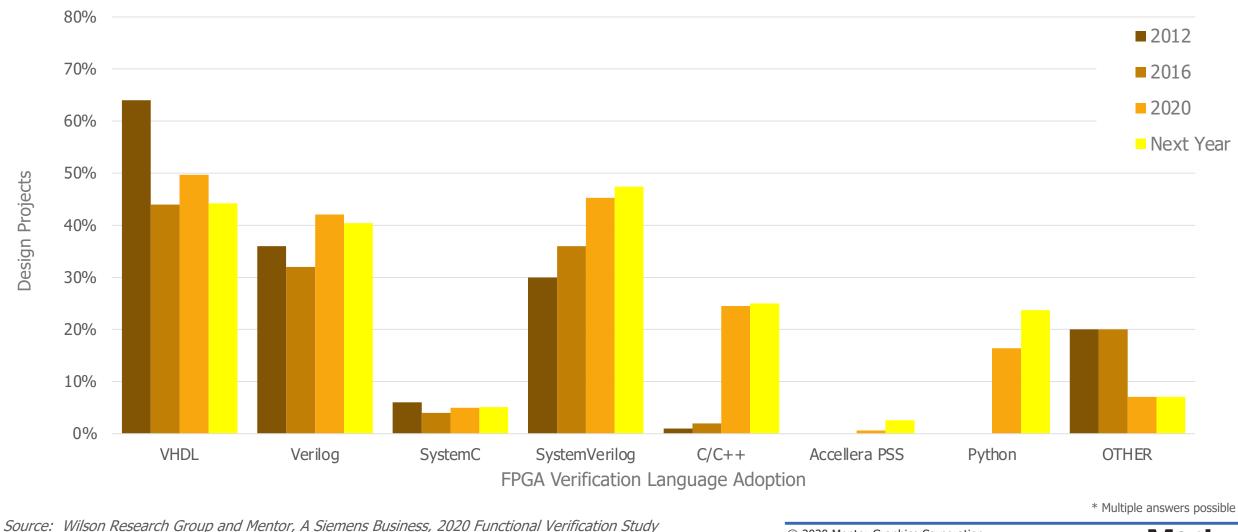

#### **FPGA Verification Language Adoption Next Twelve Months**

HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020 47

© 2020 Mentor Graphics Corporation

Me

A Siemens Business

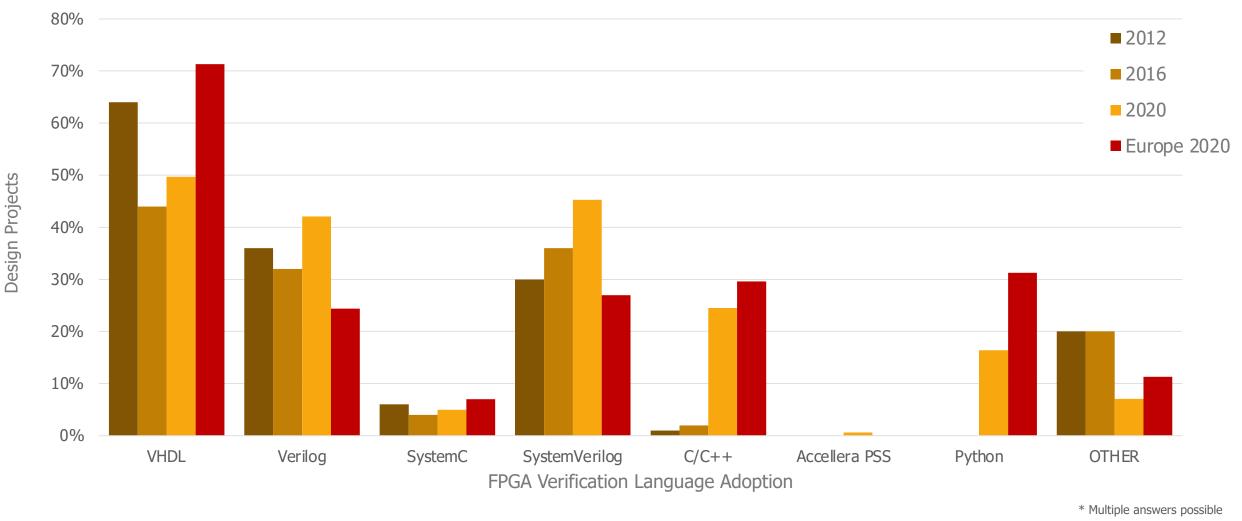

#### **FPGA Verification Language Adoption Europe**

© 2020 Mentor Graphics Corporation

Me

A Siemens Business

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

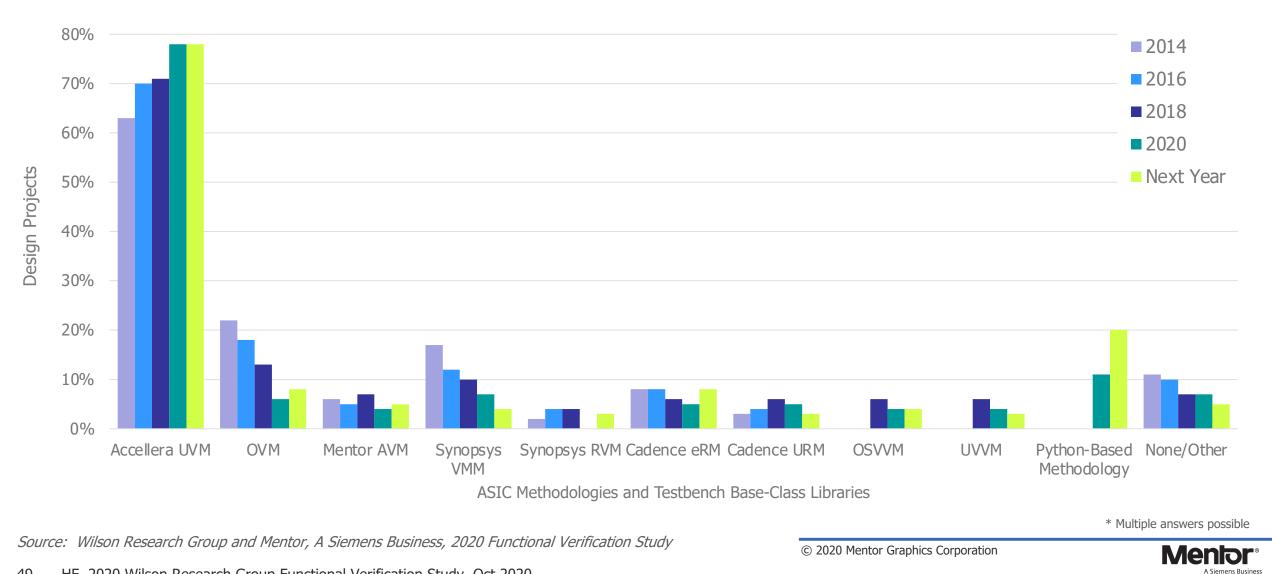

#### **ASIC Methodologies and Testbench Base-Class Libraries**

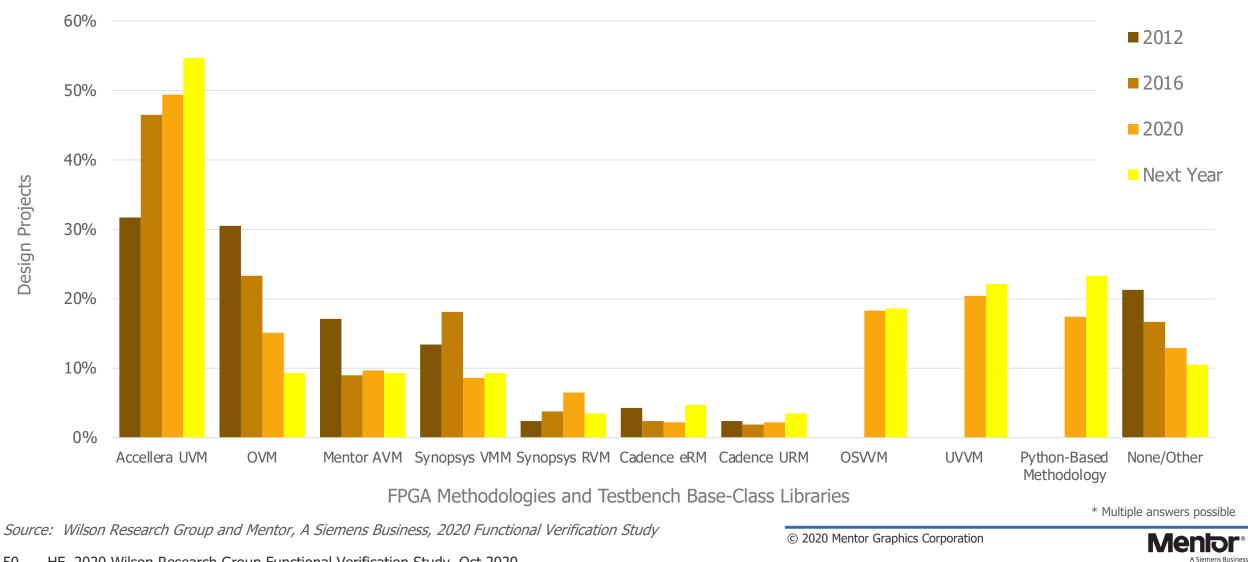

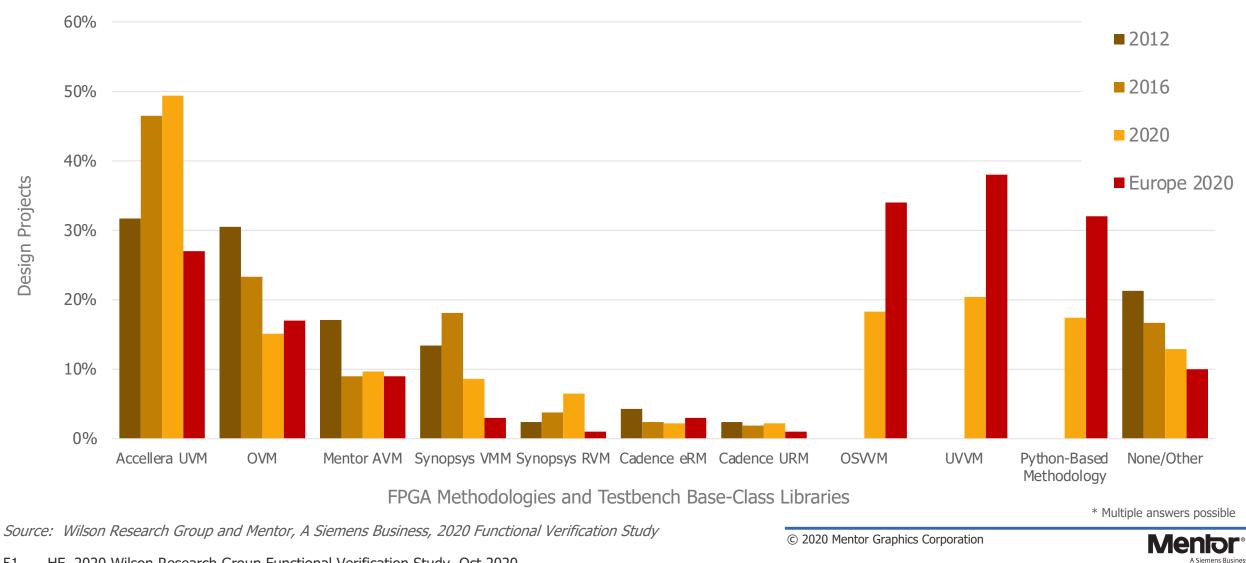

#### **FPGA Methodologies and Testbench Base-Class Libraries**

<sup>50</sup> HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

#### **FPGA Methodologies and Testbench Base-Class Libraries Europe**

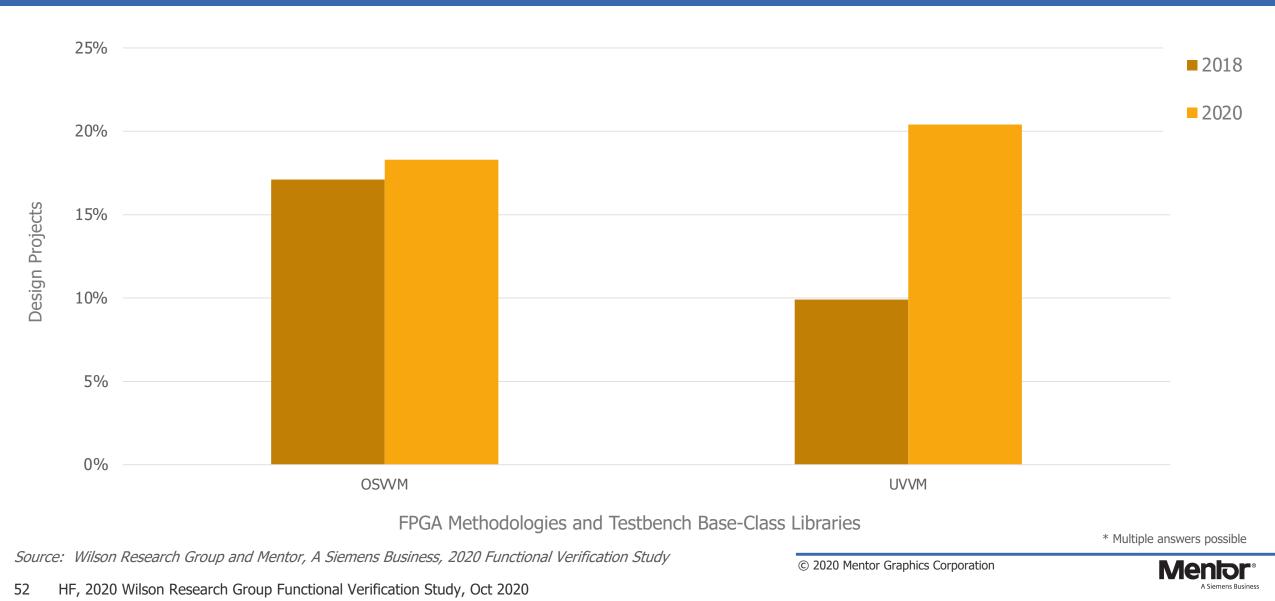

#### **FPGA OSVVM and UVVM Trends**

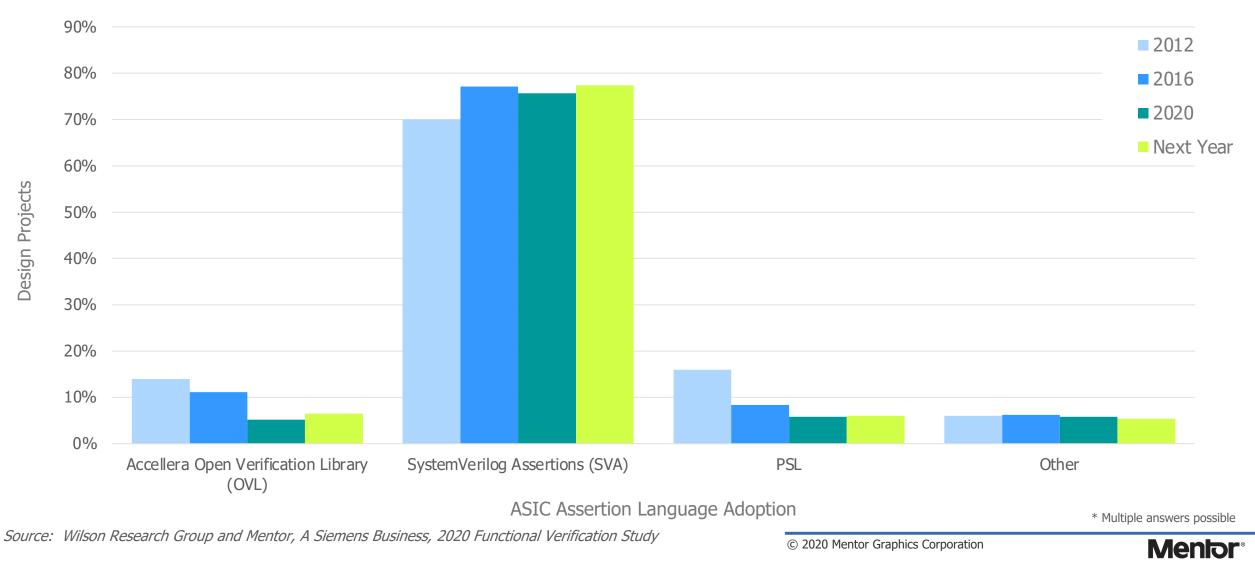

#### **ASIC Assertion Language Adoption Next Twelve Months**

A Siemens Busines

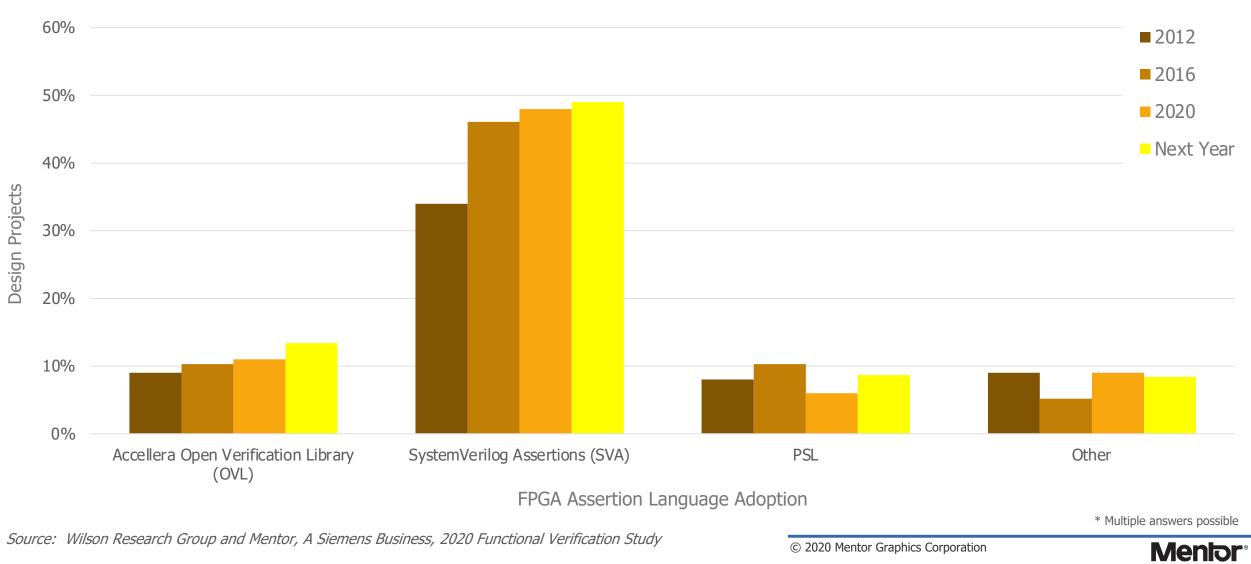

#### **FPGA Assertion Language Adoption Next Twelve Months**

A Siemens Business

# **POWER AND CLOCKING**

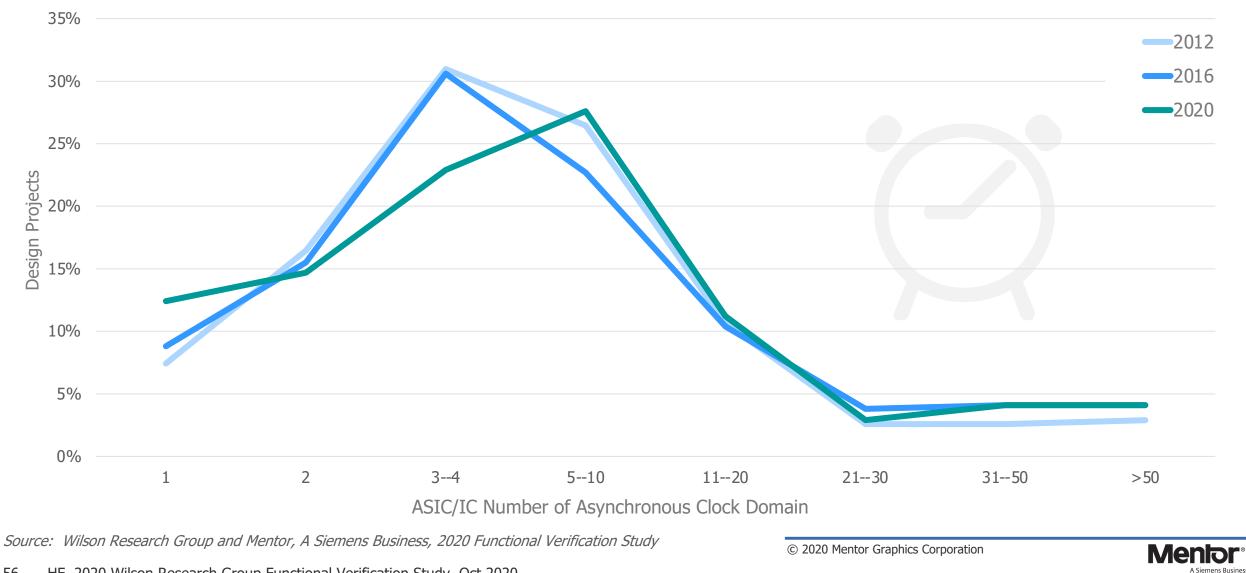

#### **ASIC/IC Number of Asynchronous Clock Domain**

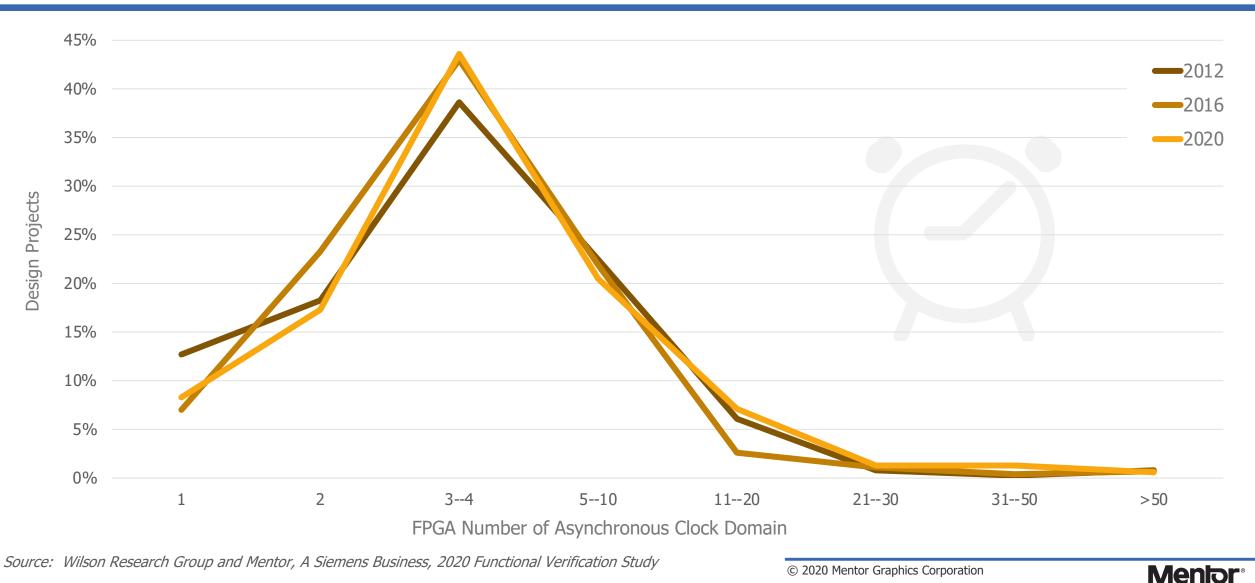

#### **FPGA Number of Asynchronous Clock Domain**

A Siemens Busines

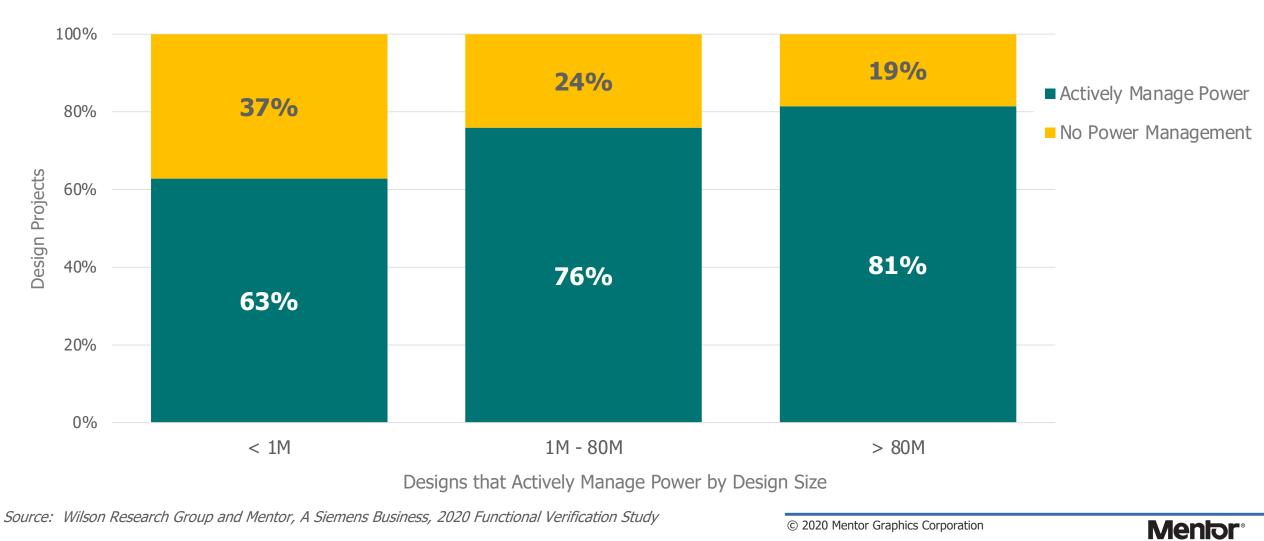

#### **ASIC/IC Actively Manage Power by Design Size**

A Siemens Business

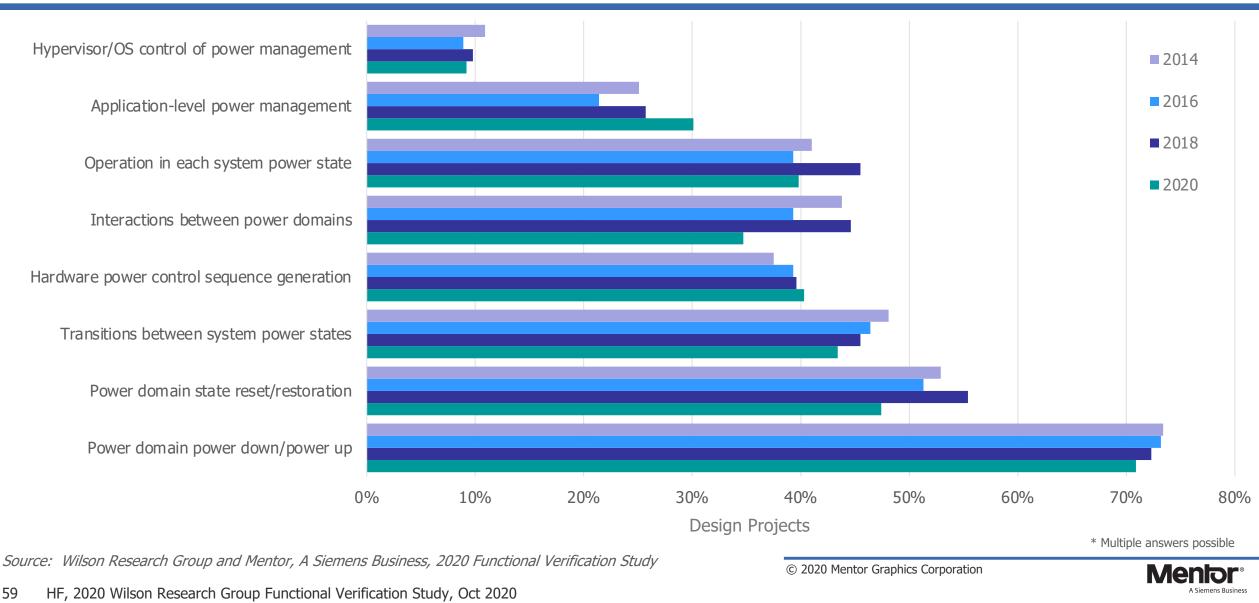

# **ASIC Power Management Features Verified**

# **VERIFICATION TECHNIQUES**

# **ASIC/IC Adoption of Formal Technology**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

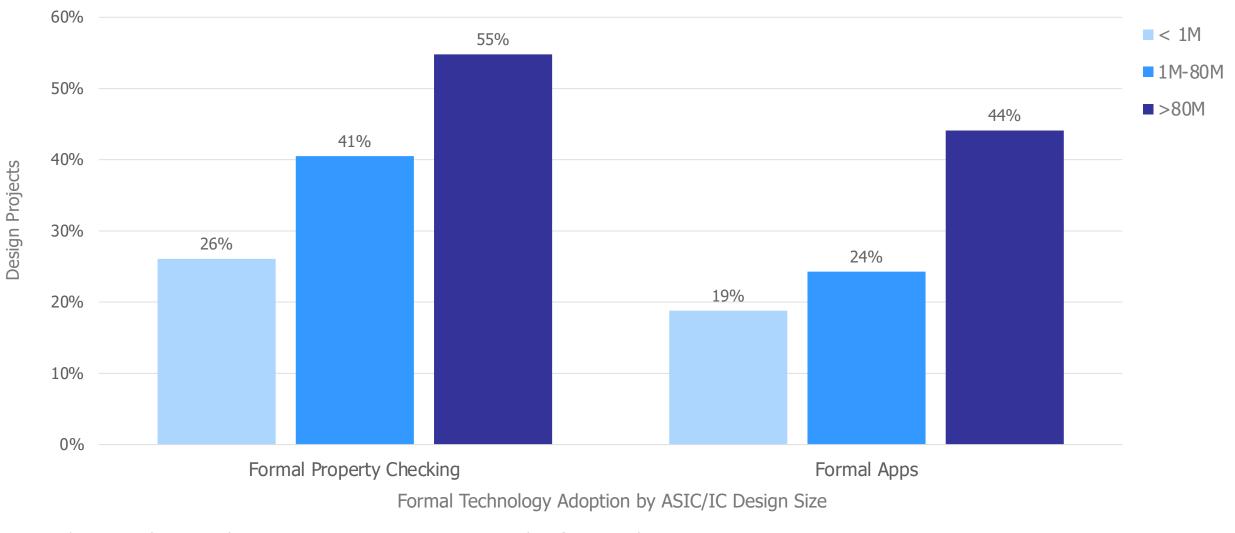

# Formal Technology Adoption by ASIC/IC Design Size

© 2020 Mentor Graphics Corporation

Men

A Siemens Busines

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

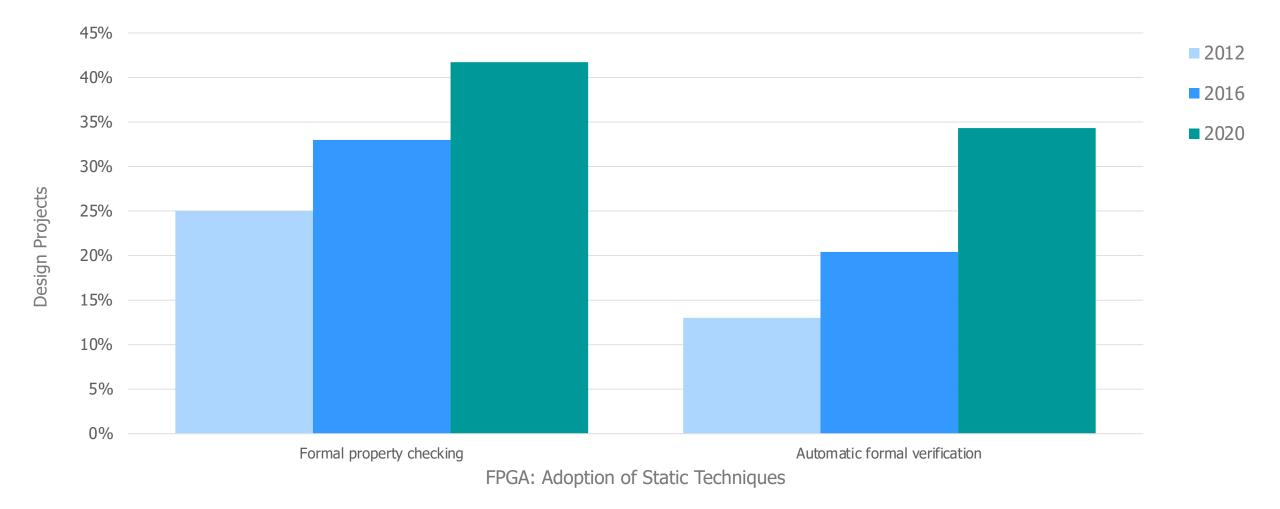

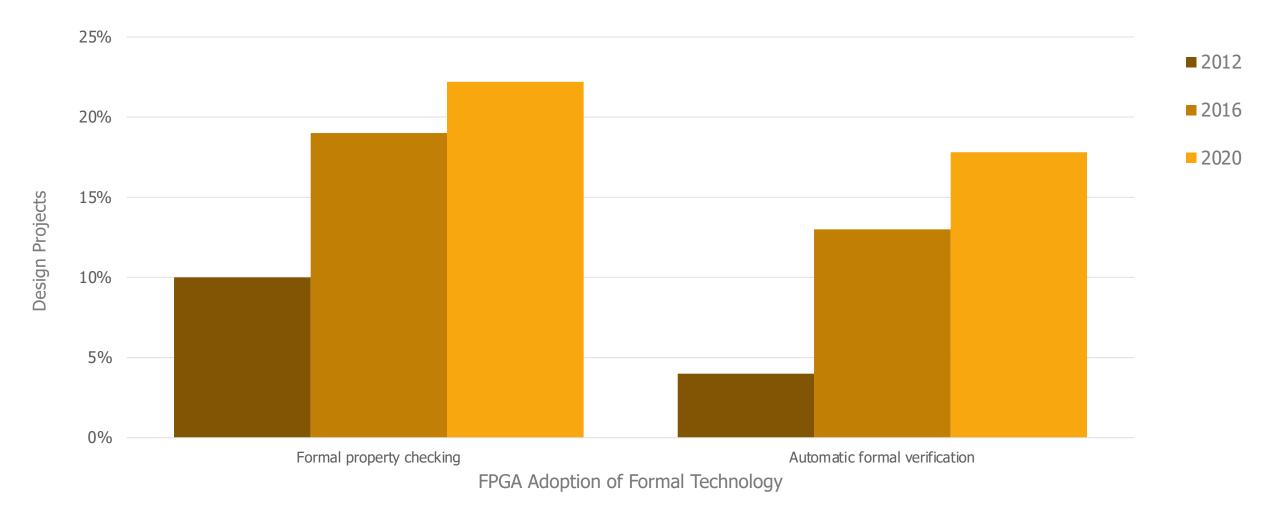

## **FPGA Adoption of Formal Technology**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

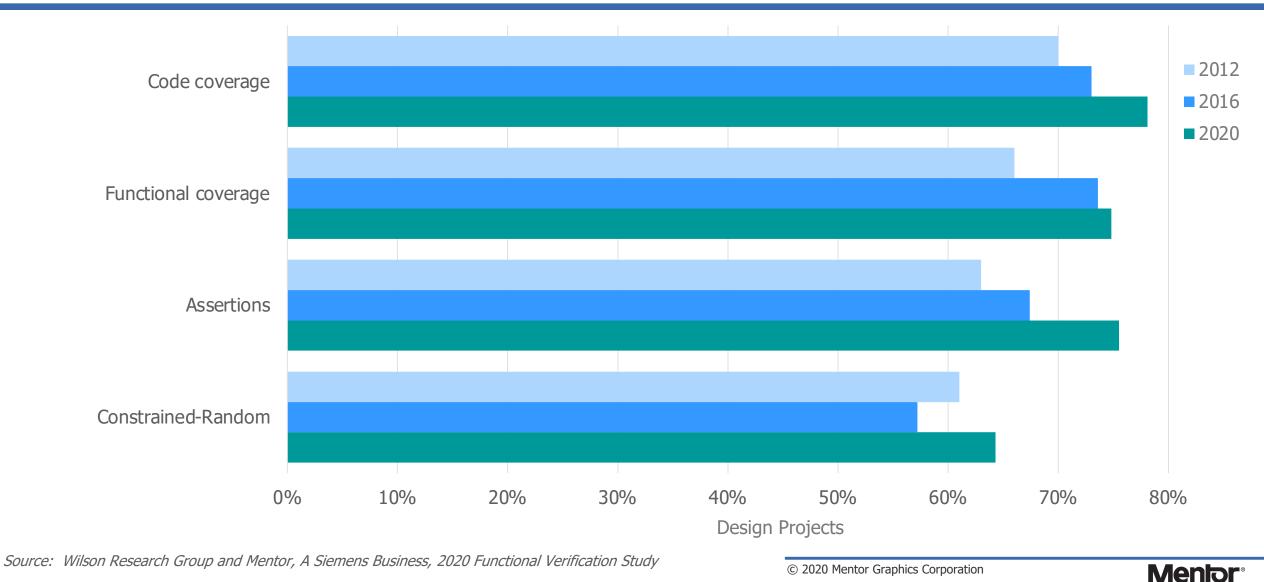

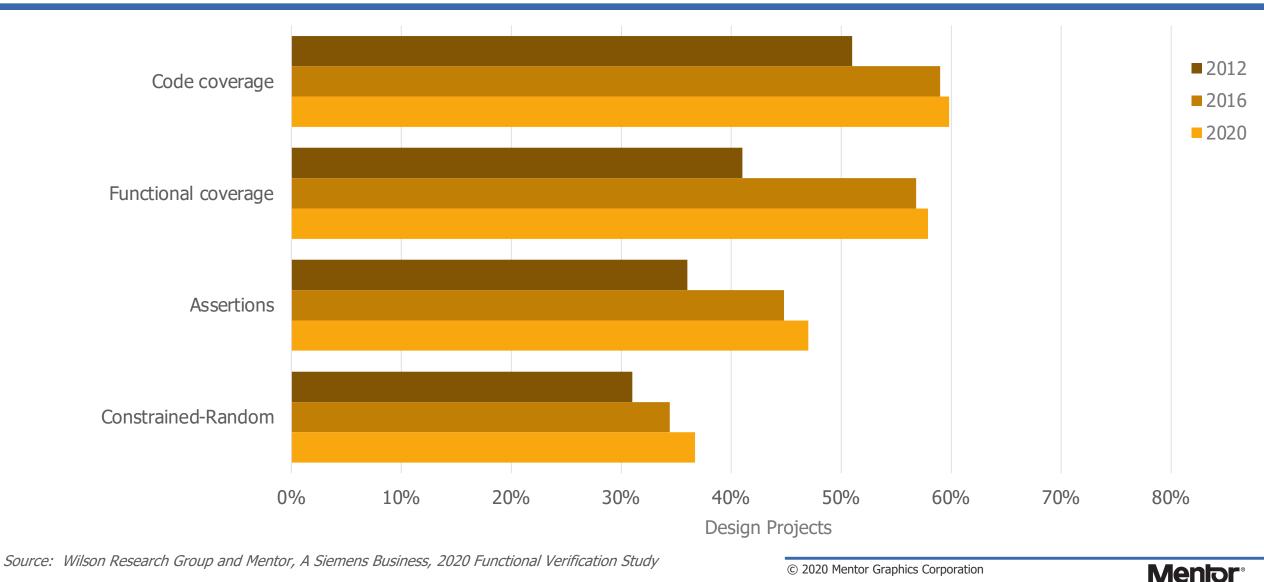

# **ASIC Adoption of Dynamic Techniques**

A Siemens Business

## **FPGA Adoption of Dynamic Techniques**

A Siemens Business

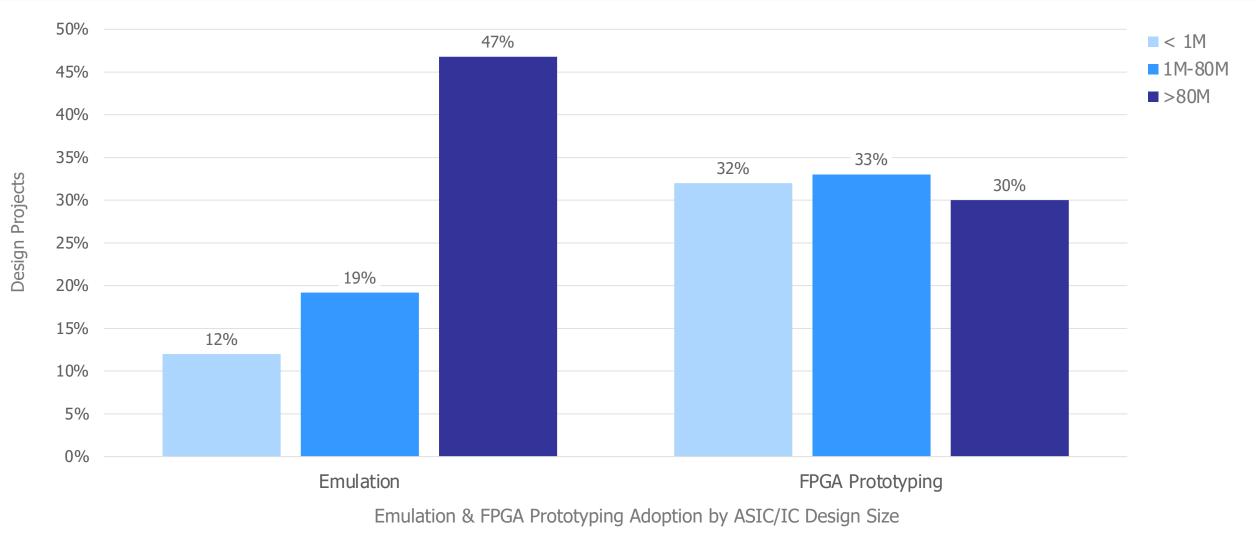

# **Emulation & FPGA Prototyping Adoption by Design Size**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

© 2020 Mentor Graphics Corporation

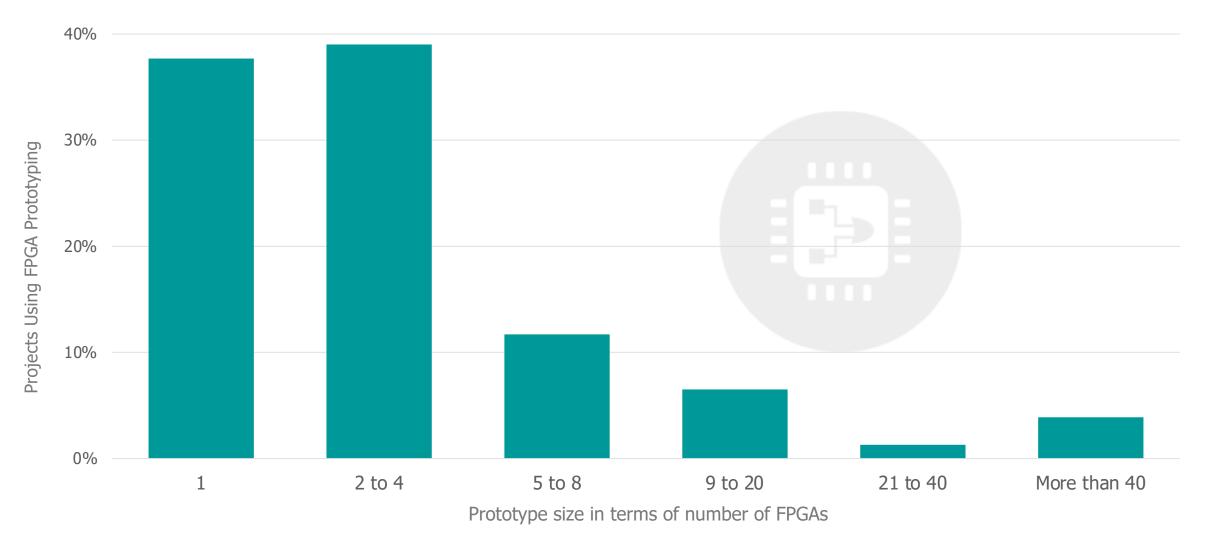

# **Prototype Size in Terms of Number of FPGAs**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

67 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

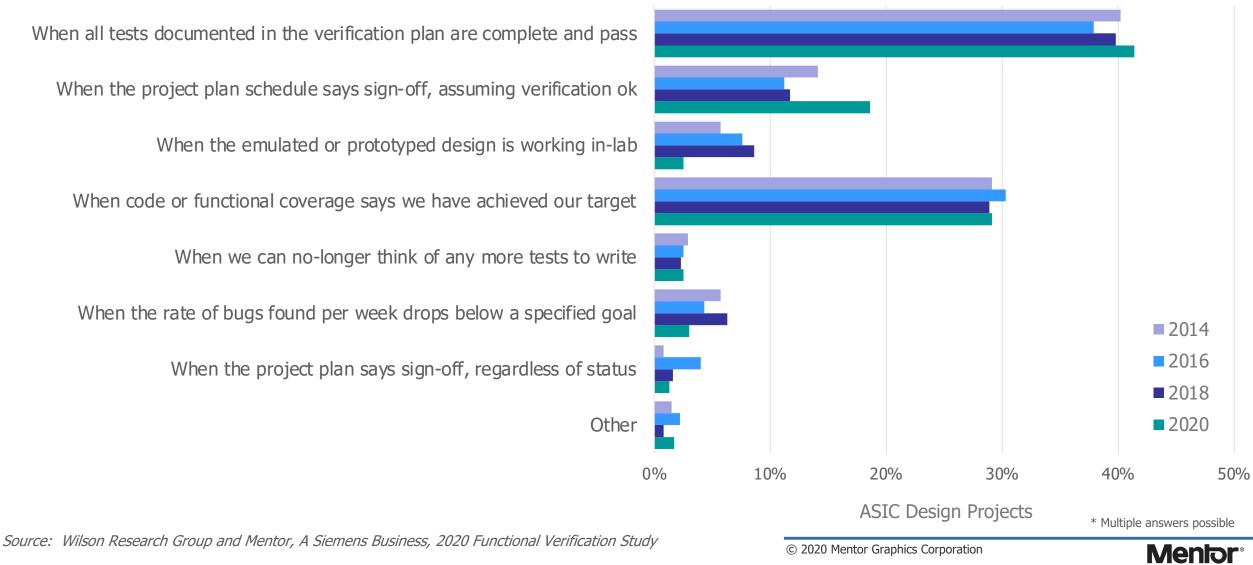

# **ASIC Signoff Criteria**

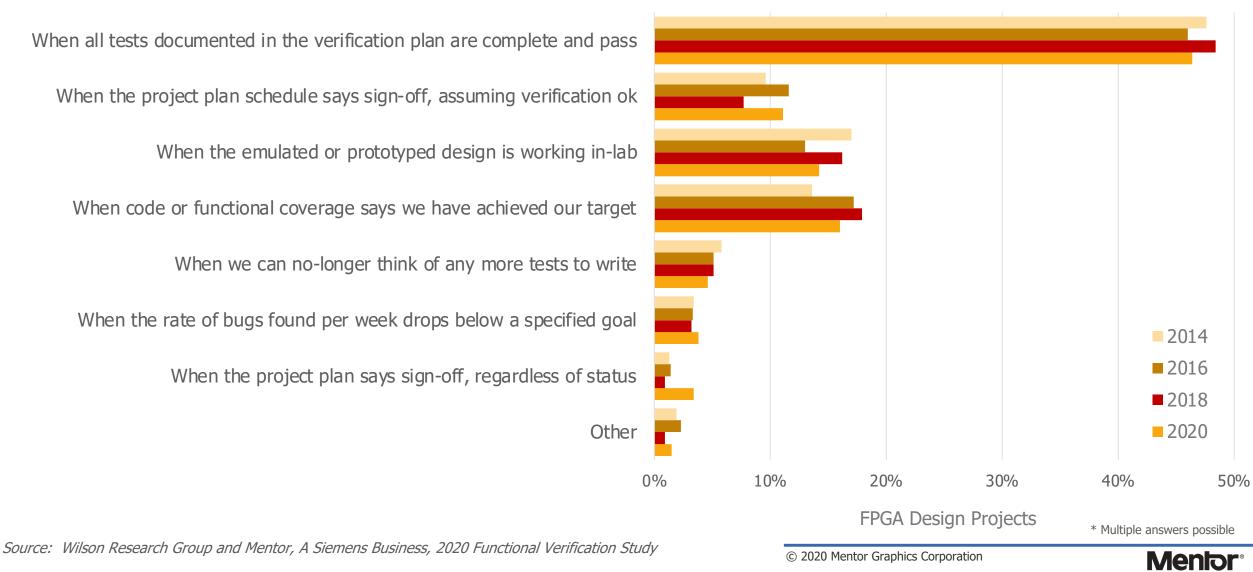

# **FPGA Signoff Criteria**

# **DOES THIS STUFF REALLY WORK?**

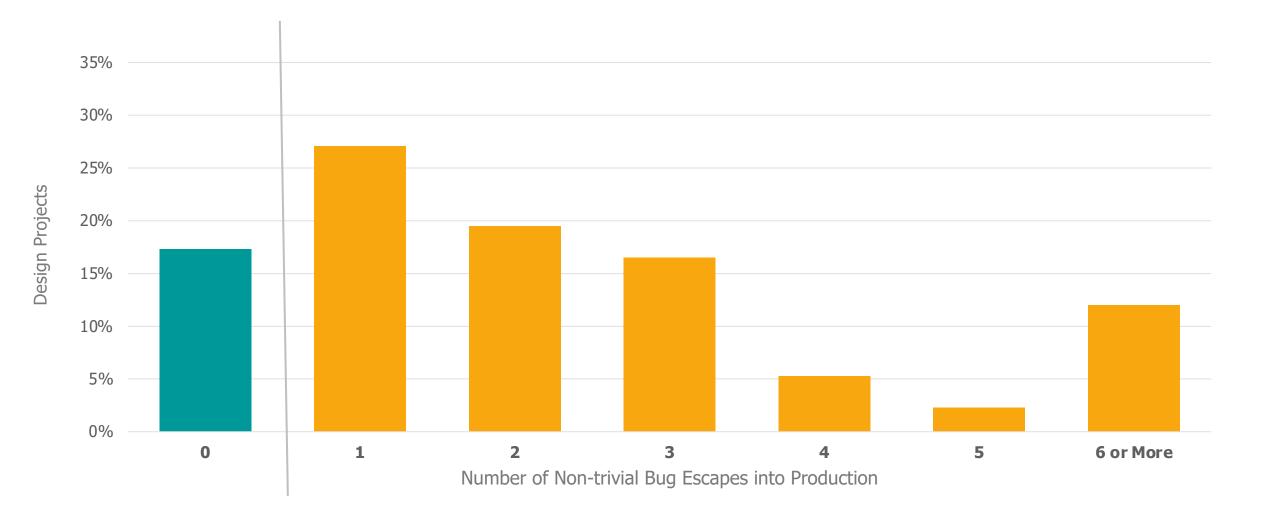

#### **Number of Non-trivial FPGA Bug Escapes into Production**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

#### **Number of Non-trivial FPGA Bug Escapes into Production**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

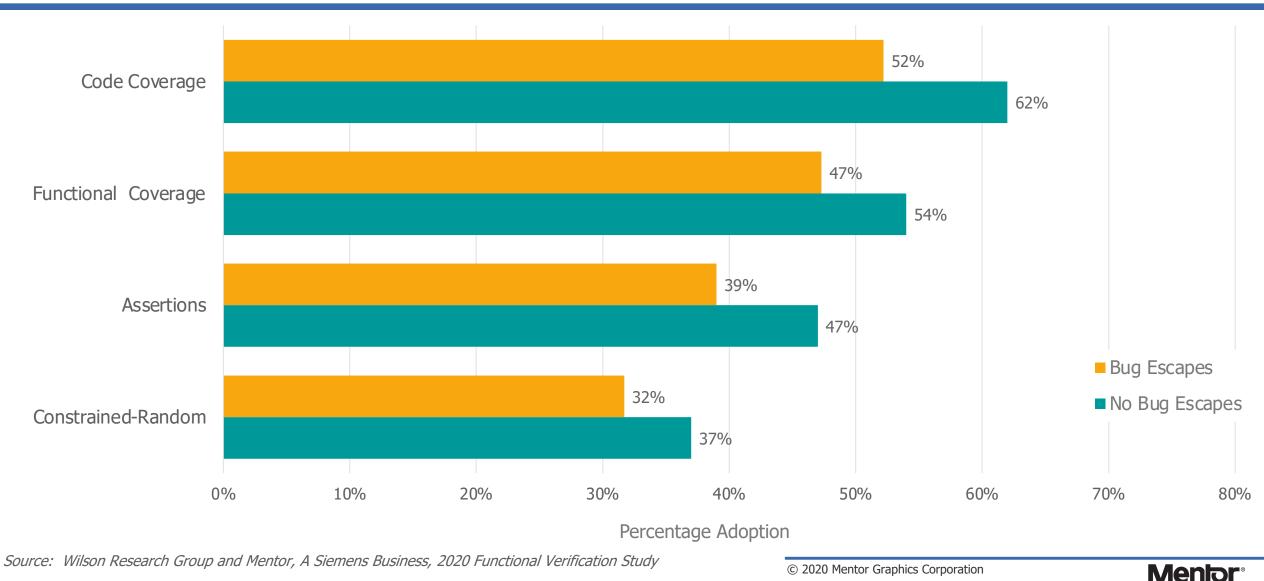

#### **2020 FPGA Verification Technique Adoption and Bug Escapes**

A Siemens Business

# **BIGGEST CHALLENGES**

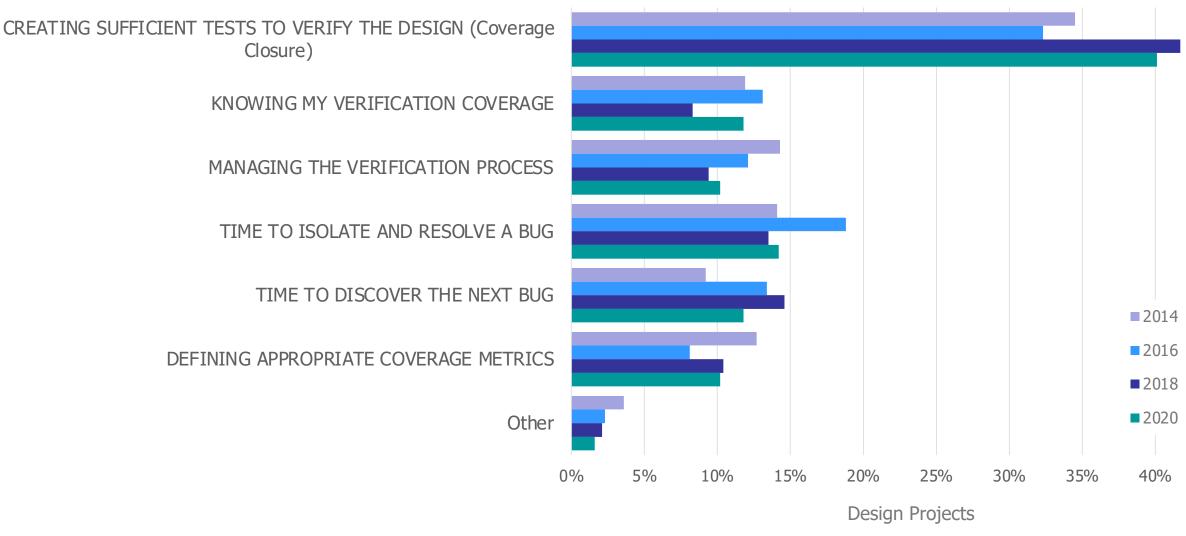

# **ASIC Biggest Functional Verification Challenge**

Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study

75 HF, 2020 Wilson Research Group Functional Verification Study, Oct 2020

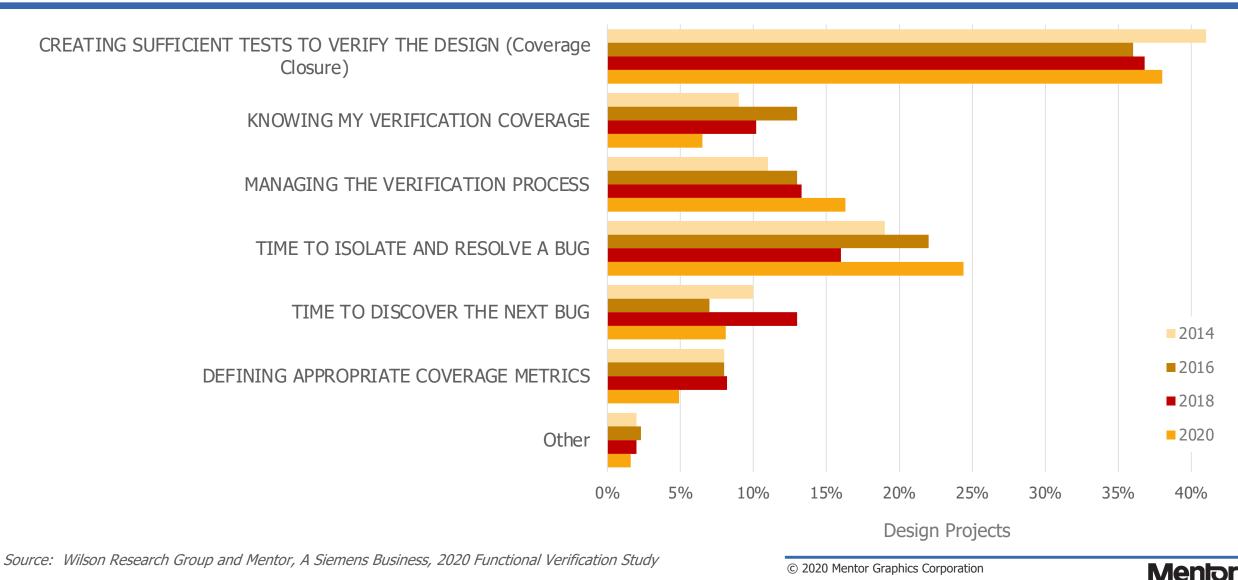

# **FPGA Biggest Functional Verification Challenge**

Siemens Busines

# SUMMARY

- Increased requirements driving complexity

- IC/ASIC projects mature in their processes

- FPGA projects are being forced to mature their processes

- Fewer bug escapes occur in project's with mature verification processes

# **2020 Functional Verification Reports**

# Verification Academy

The most comprehensive resource for verification training

#### **Industry Data and Surveys**

80

Every two years, Mentor Graphics commissions Wilson Research Group to

conduct a broad, vendor-

independent survey of design verification practices around the world. Results of the functional verification study demonstrate an ongoing convergence of design and verification practices toward a common methodology.

#### Sessions

#### Functional Verification Study - 2018

Harry Foster highlights the key findings from the 2018 Wilson **Research Group Functional**

Verification Study, and provides his

interpretation and analysis behind today's emerging trends.

#### Functional Verification Study - 2016

findings.

Harry Foster discusses the results from the 2016 Wilson Research Group Functional Verification Study, and provides some insight into its

#### ASIC/IC Trends in Functional Verification - 2014

Harry Foster discusses the ASIC/IC verification trends from the 2014 Wilson Research Group Functional Verification Study, and provides

some insight into its findings.

#### FPGA Trends in Functional Verification - 2014

Harry Foster discusses the FPGA verification trends from the 2014 Wilson Research Group Functional Verification Study, and provides

some insight into its findings.

# A Siemens Business

www.mentor.com