## COMS30026 Design Verification **Functional Formal Verification** Kerstin Eder

#### **Trustworthy Systems Laboratory**

https://www.bristol.ac.uk/engineering/research/trustworthy-systems-laboratory/

(Acknowledgement: I gratefully acknowledge the support from Cadence who provide the licenses for the Formal Verification Tool demonstration. Special thanks also to Anton Klotz from the Cadence Academic Network.)

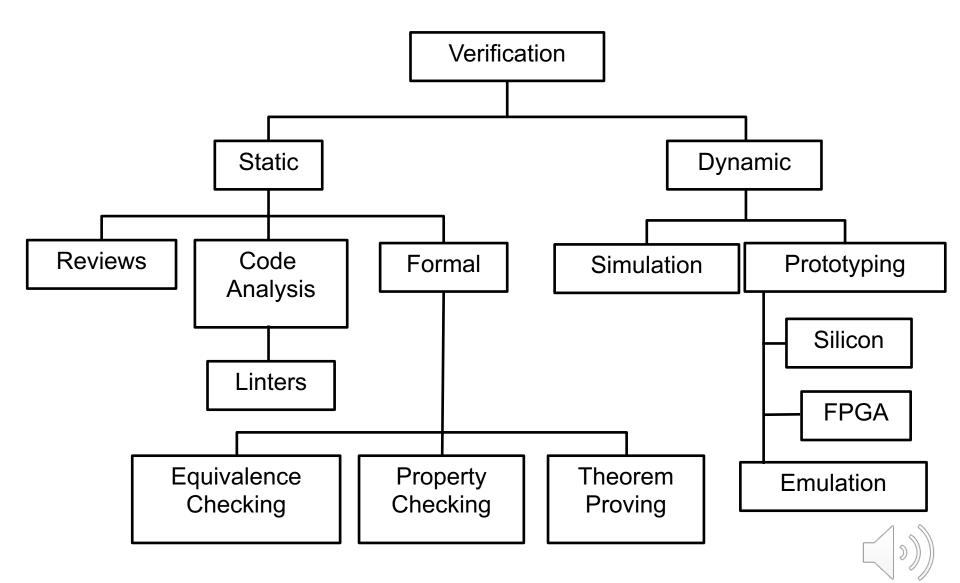

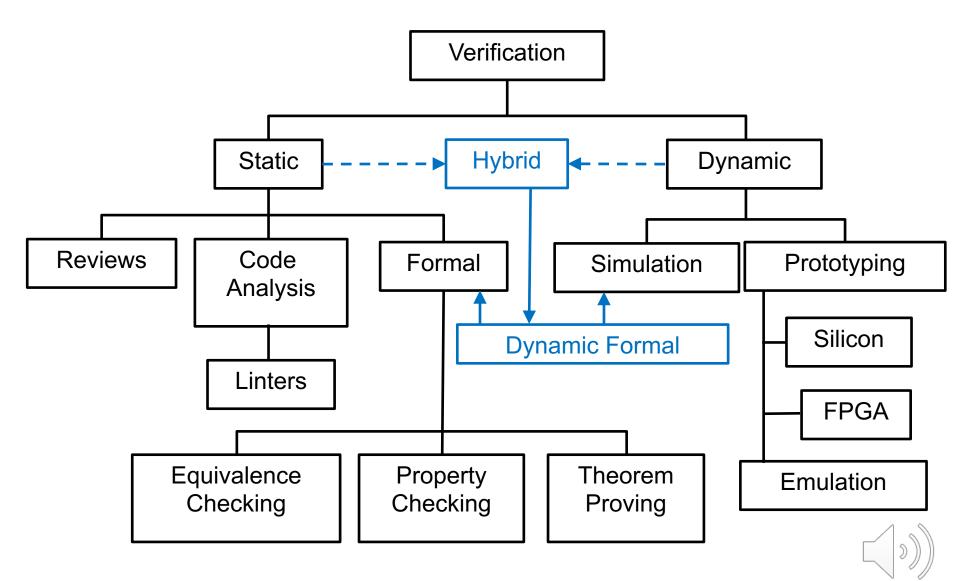

#### **Functional Verification Approaches**

#### **Functional Verification Approaches**

#### **Formal Property Checking**

# Properties of a design (aka assertions) are formally proven or disproved.

- Used to complement simulation-based verification.

- Usually employed at **lower levels** in the design hierarchy.

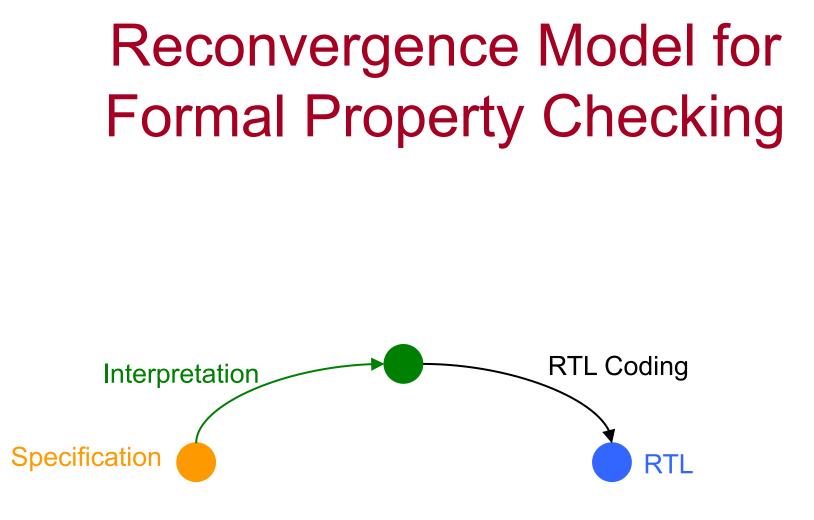

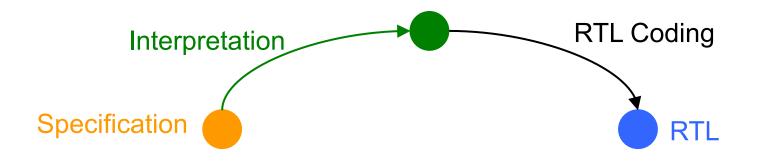

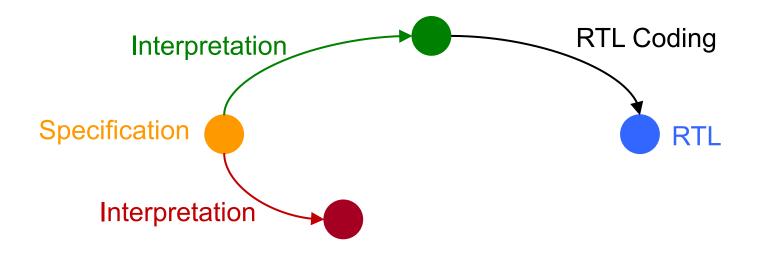

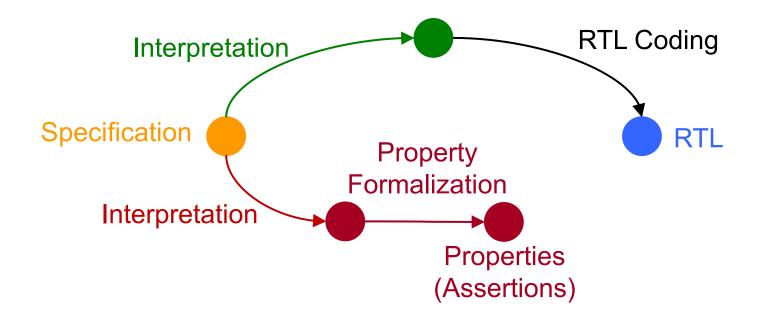

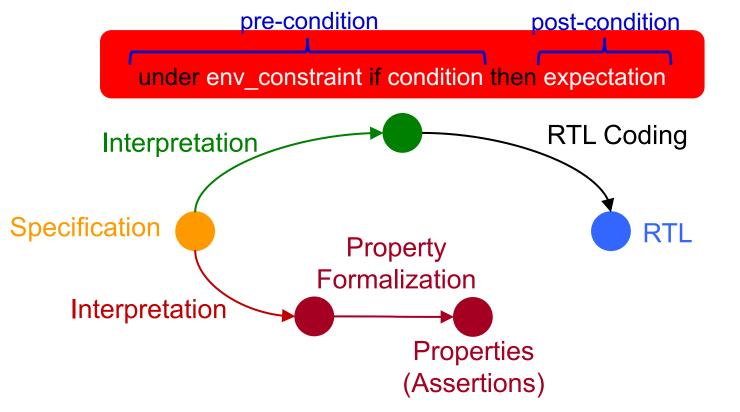

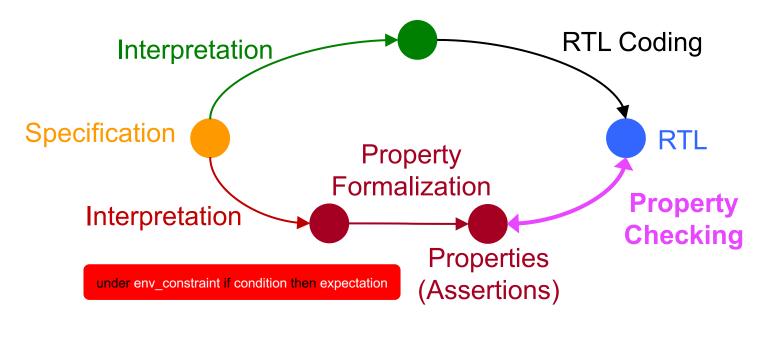

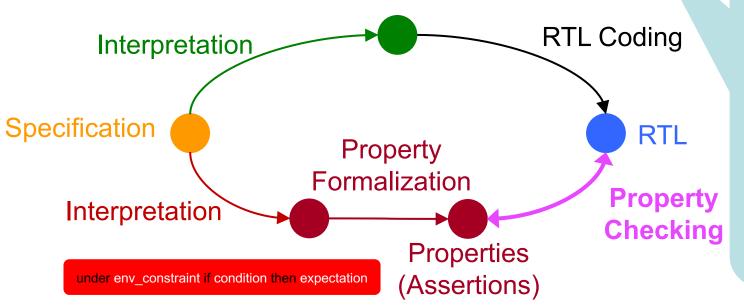

Give a reconvergence model for formal property checking!

A reconvergence model is a conceptual representation of the verification process. It helps us understand what is being verified

- **Properties** are derived from the specification. (interpretation step)

- Properties are expressed as formulae in some (temporal) logic.

- **Properties** are derived from the specification. (interpretation step)

- Properties are expressed as formulae in some (temporal) logic.

- **Properties** are derived from the specification. (interpretation step)

- Properties are expressed as formulae in some (temporal) logic.

Properties are derived from the specification. (interpretation step)

Properties are expressed as formulae in some (temporal) logic.

- **Properties** are derived from the specification. (interpretation step)

- Properties are expressed as formulae in some (temporal) logic.

- Checking is typically performed on a Finite State Machine model of the design.

- This may be an FSM model of the RTL (as shown in the example).

- **Properties** are derived from the specification. (interpretation step)

- Properties are expressed as formulae in some (temporal) logic.

- Checking is typically performed on a Finite State Machine model of the design.

This may be the RTL (as shown in the example).

There are also Model Checkers for software, e.g. C, C++ and Java.

https://en.wikipedia. org/wiki/List\_of\_mod el\_checking\_tools

#### **Overview of Formal Property Checking**

- Property Checking is the most common form of high-level formal verification used in practice.

- Property checking is fully automatic.

Requires the properties to be written.

- It performs exhaustive verification of the design wrt the specified properties.

- It provides proofs and can demonstrate the absence of bugs.

- A counterexample is presented for failed properties.

- Frequently used for critical, well specified parts of the design, e.g. cache coherence protocols, bus protocols, interrupt controllers, interfaces

#### **Scalability of Formal Verification**

Due to the fact that formal verification is exhaustive, formal methods can suffer from capacity limits. INFORMATION AND COMPUTATION 98, 142-170 (1992)

#### Symbolic Model Checking: 10<sup>20</sup> States and Beyond\*

J. R. BURCH, E. M. CLARKE, AND K. L. MCMILLAN

School of Computer Science, Carnegie Mellon University, Pittsburgh, Pennsylvania 15213

AND

D. L. DILL AND L. J. HWANG

Stanford University, Stanford, California 94305

Many different methods have been devised for automatically verifying finite state systems by examining state-graph models of system behavior. These methods all depend on decision procedures that explicitly represent the state space using a list or a table that grows in proportion to the number of states. We describe a general method that represents the state space symbolically instead of explicitly. The generality of our method comes from using a dialect of the Mu-Calculus as the primary specification language. We describe a model checking algorithm for Mu-Calculus formulas that uses Bryant's Binary Decision Diagrams (Bryant, R. E., 1986, IEEE Trans. Comput. C-35) to represent relations and formulas. We then show how our new Mu-Calculus model checking algorithm can be used to derive efficient decision procedures for CTL model checking, satisfiability of linear-time temporal logic formulas, strong and weak observational equivalence of finite transition systems, and language containment for finite  $\omega$ -automata. The fixed point computations for each decision procedure are sometimes complex, but can be concisely expressed in the Mu-Calculus. We illustrate the practicality of our approach to symbolic model checking by discussing how it can be used to verify a simple synchronous pipeline circuit. © 1992 Academic Press, Inc.

J.R. Burch, E.M. Clarke, K.L. McMillan, D.L. Dill, L.J. Hwang. Symbolic modchecking: 1020 States and beyond, Information and Computation, Volume 9 2, 1992, Pages 142-170, ISSN 0890-5401. https://doi.org/10.1016/0890-5401(92)90017-A

e

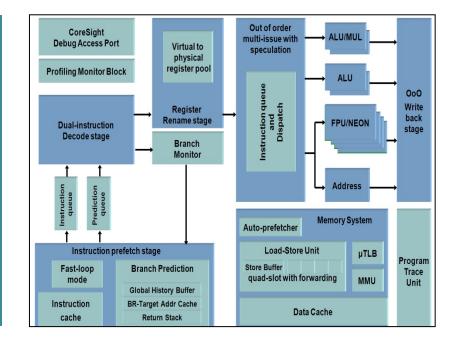

- Consider simulating a typical CPU design

- 500k gates, 20k DFFs, 500 inputs

- 70 billion simulation cycles,

running on 200 linux boxes for a week

- How big: 2<sup>36</sup> cycles

- Consider simulating a typical CPU design

- 500k gates, 20k DFFs, 500 inputs

- 70 billion sim cycles,

running on 200 linux boxes for a week

- How big: 2<sup>36</sup> cycles

- Consider formally verifying this design

- Input sequences: cycles 2<sup>(inputs+state)</sup> = 2<sup>20500</sup>

- What about X's: 2<sup>15000</sup> (5,000 X-assignments + 10,000 non-reset DFFs)

- How big: 2<sup>20500</sup> cycles (2<sup>15000</sup> combinations of X is not significant here!)

- Consider simulating a typical CPU design

- 500k gates, 20k DFFs, 500 inputs

- 70 billion sim cycles, running on 200 linux boxes for a week

- How big: 2<sup>36</sup> cycles

- Consider formally verifying this design

- Input sequences: cycles 2<sup>(inputs+state)</sup> = 2<sup>20500</sup>

- What about X's: 2<sup>15000</sup> (5,000 X-assignments + 10,000 non-reset DFFs)

- How big: 2<sup>20500</sup> cycles (2<sup>15000</sup> combinations of X is not significant here!)

- These are a big numbers!

- Cycles to simulate the 500k gate CPU design: 2<sup>36</sup>

- Cycles to formally verify a 32-bit adder:

- Number of stars in universe:

(70 billion) (18 billion billion) (10<sup>22</sup>)

264

274

- Consider simulating a typical CPU design

- 500k gates, 20k DFFs, 500 inputs

- 70 billion sim cycles, running on 200 linux boxes for a week

- How big: 2<sup>36</sup> cycles

- Consider formally verifying this design

- Input sequences: cycles 2<sup>(inputs+state)</sup> = 2<sup>20500</sup>

- What about X's: 2<sup>15000</sup> (5,000 X-assignments + 10,000 non-reset DFFs)

- How big: 2<sup>20500</sup> cycles (2<sup>15000</sup> combinations of X is not significant here!)

- These are a big numbers!

- Cycles to simulate the 500k gate CPU design:  $2^{36}$

- Cycles to formally verify a 32-bit adder:

- Number of stars in universe:

- Number of atoms in the universe:

- Possible X combinations in 500k gate design:

- Cycles to formally verify the 500k gate design:

- $2^{36}$ (70 billion) $2^{64}$ (18 billion billion) $2^{74}$ (10<sup>22</sup>) $2^{260}$ (10<sup>78</sup>) $2^{15000}$ (10<sup>4515</sup> x 3) $2^{20500}$ (10<sup>6171</sup>)

#### Managing complexity in FV

- There are tried and trusted techniques to overcome the capacity limitations of FV:

- Start with narrow focus on block level, work up towards higher levels in the design hierarchy turning proven assertions into assumptions

- Restrict property checking to work over finite small time windows.

- Limit environment behaviour by strengthening constraints.

- Case splits over a set of properties, partitioning and black boxing.

#### **Functional Verification Approaches**

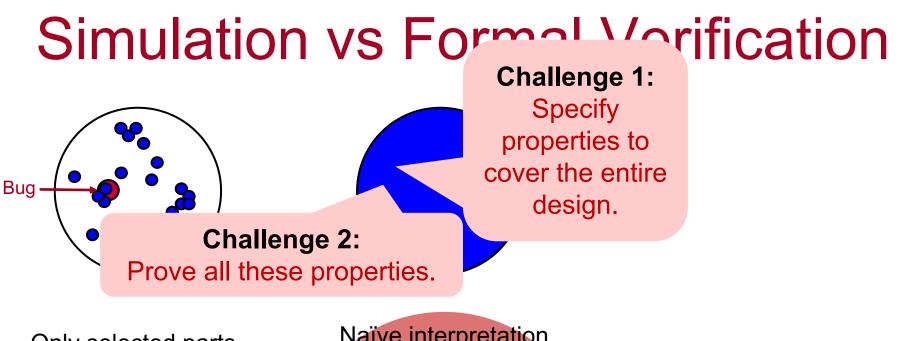

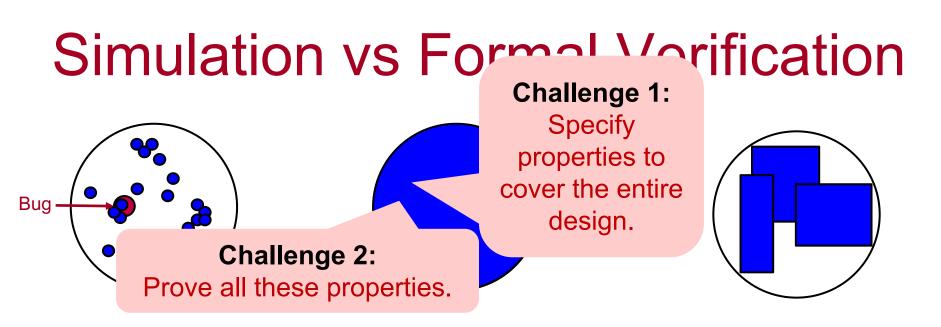

#### Simulation vs Formal Verification

Only selected parts of the design can be covered during simulation.

[B. Wile , J.C. Goss and W. Roesner, "Comprehensive Functional Verification – The Complete Industry Cycle", Morga Kaufman, 2005]

Only selected parts of the design can be covered during simulation. Naïve interpretation of exhaustive formal verification: Verify ALL properties.

[B. Wile , J.C. Goss and W. Roesner, "Comprehensive Functional Verification – The Complete Industry Cycle", Morga Kaufman, 2005]

Only selected parts of the design can be covered during simulation. Naïve interpretation of exhaustive formal verification: Verify ALL properties.

In practice, completeness issues and capacity limits restrict formal verification to selected parts of the design.

[B. Wile , J.C. Goss and W. Roesner, "Comprehensive Functional Verification – The Complete Industry Cycle", Morga Kaufman, 2005]

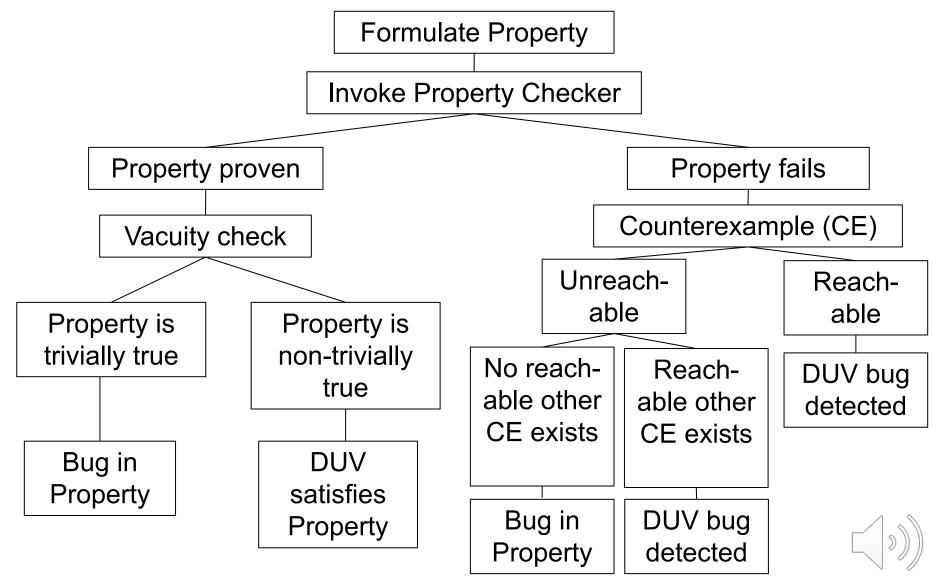

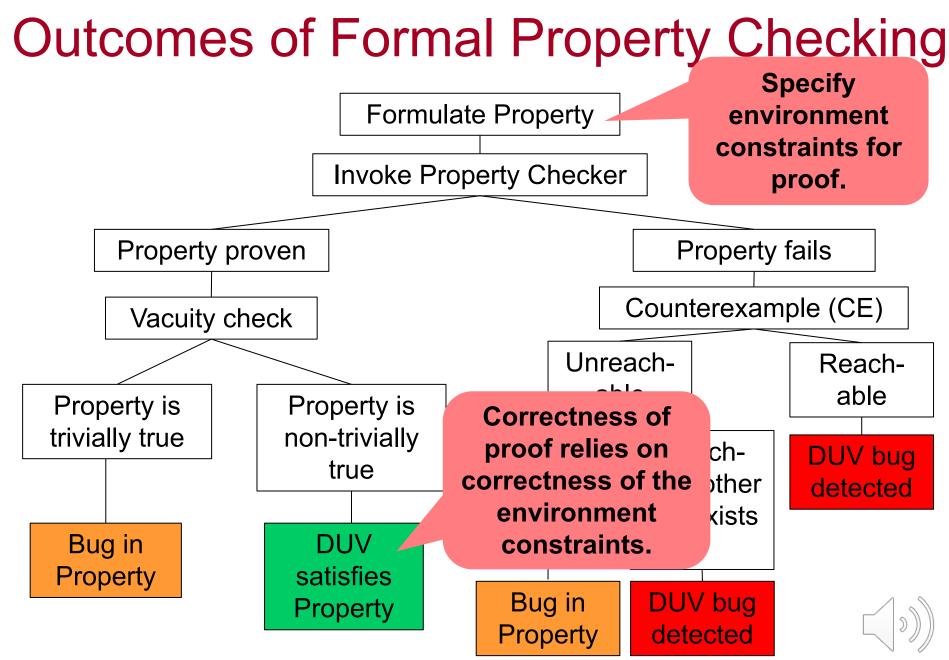

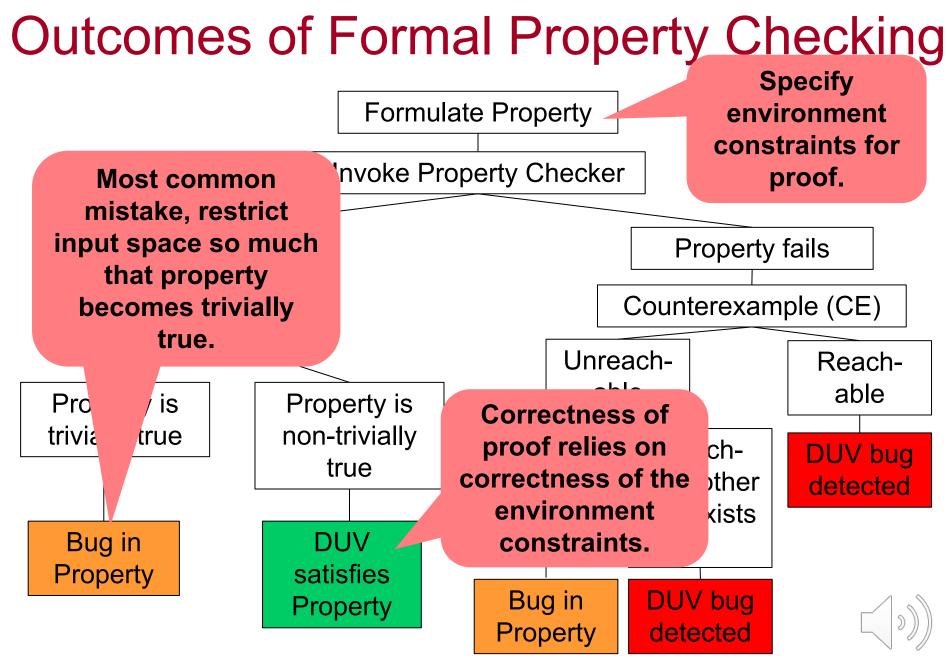

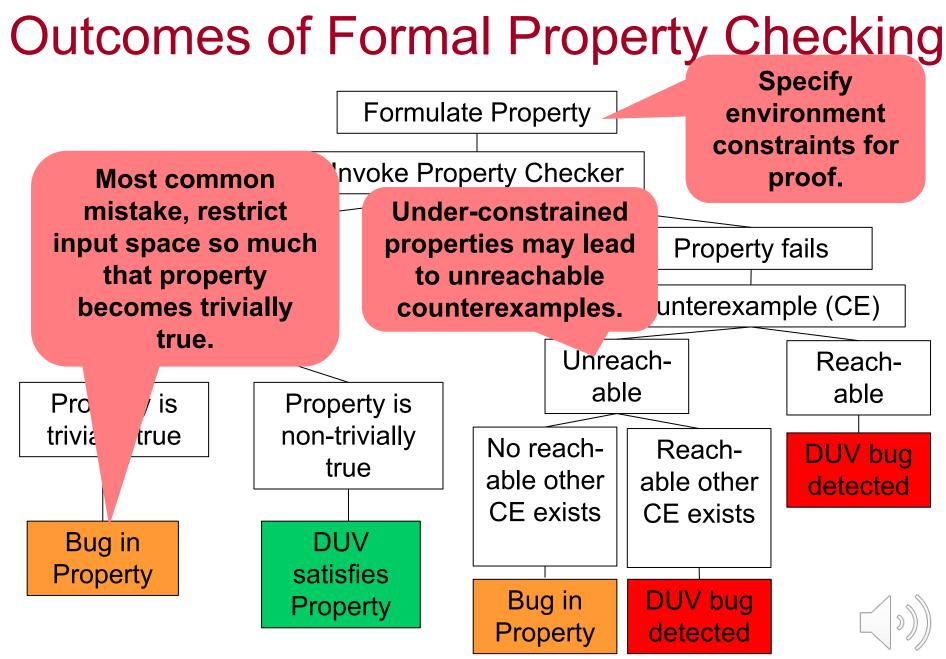

#### **Outcomes of Formal Property Checking**

#### How do you know you've encoded the property right?

- Keep properties and sequences simple; build complex properties from simple, short properties.

- Peer review properties you write.

- Know what to expect, e.g. create failing conditions.

- If the property fails (when you expect it to succeed), then investigate the counterexample:

– Is it reachable or not?

But if the property succeeds, how do you know whether you've encoded the property right?

#### HANDS-ON FORMAL PROPERTY CHECKING DEMO

#### **Formal Property Checking**

#### Jasper DEMO

- DUV: FIFO design from ABV lecture

- Verification of selected FIFO properties from ABV

| 000                                                                                           | X (session_0) - Jaspe                       | Isession_0) - JasperGold Apps (/sessionLogs/session_0) - ProofGrid Manager        |                                  |                     |                                          |                                             |        |            |        |              |                        |      |        |                            |           |                                   |            |         |        |            |               |

|-----------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|---------------------|------------------------------------------|---------------------------------------------|--------|------------|--------|--------------|------------------------|------|--------|----------------------------|-----------|-----------------------------------|------------|---------|--------|------------|---------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew                                                        | <u>D</u> esign <u>R</u> eports <u>A</u> ppl | <u>F</u> ile <u>T</u> ools <u>P</u> lot Ta <u>b</u> s <u>W</u> indow <u>H</u> elp |                                  |                     |                                          |                                             |        |            |        |              |                        |      |        |                            | cādei     | n c e'                            |            |         |        |            |               |

| Formal Property                                                                               |                                             |                                                                                   | Disable 🕡 😳 🍽 🖾 Ĺ, 🧔             |                     |                                          |                                             |        |            |        |              |                        |      |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               |                                             |                                                                                   | <embedded> (thread 0)</embedded> |                     |                                          |                                             |        |            |        |              |                        |      |        |                            |           |                                   |            |         |        |            |               |

| Design Hierarch × Property Table                                                              |                                             | 76 🥶                                                                              | ] ŷ- Filter on name              |                     |                                          |                                             |        |            |        |              |                        |      |        |                            |           |                                   | <b>•</b> ( | 0.Hp    |        |            |               |

| fifo (fifo)                                                                                   | K C Tre Filter on na                        | Туре                                                                              | Name                             | Y                   | PRE                                      | Нр                                          |        | Ht         | N      | В            |                        | -    |        |                            |           |                                   |            | 0.В     | 00.Htp | - 0        | 0.Ht          |

|                                                                                               | News                                        | Assert                                                                            | valid_cnt_ra                     | nge_top             |                                          | Ŷ1                                          | 15)    | 2 14       | Ø      | ? 1          | 14 -                   | -    |        |                            |           |                                   |            |         | 0.N    |            |               |

|                                                                                               |                                             |                                                                                   | valid_cnt_ra                     |                     | <b>~</b>                                 |                                             |        |            |        |              |                        | - 5  |        |                            |           |                                   |            |         |        |            |               |

| <u>ч                                    </u>                                                  | assume:0                                    |                                                                                   | mutex_full_                      |                     |                                          | 🖋 (-,                                       |        |            |        |              | អ <sup>12 -</sup>      | -    |        |                            |           |                                   |            |         |        | <b>–</b> ( | 0.B           |

|                                                                                               |                                             |                                                                                   |                                  | r_clear_wrong       |                                          | ? (1,                                       |        |            |        |              | , np                   |      |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               | valid_cnt_range_botto                       |                                                                                   |                                  |                     |                                          | <ul><li>✓ (1,</li></ul>                     | -      | 28         |        |              | <b>1</b> 0 -           |      |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               | mutex_full_empty                            |                                                                                   |                                  | lear_ignore_write   |                                          | ✓ (1,                                       |        | 28         |        |              | at                     |      |        |                            |           | ┍┙╴┍┘                             |            |         |        |            |               |

|                                                                                               | empty_after_clear_wr<br>empty_after_clear   |                                                                                   |                                  |                     |                                          | ✓ (1,                                       |        | 28         |        |              | Proof / Trace attempts |      |        |                            |           | JJ                                |            |         |        |            |               |

|                                                                                               | empty_after_clear iq                        |                                                                                   | empty_one_                       |                     |                                          | <b>?</b> (1,                                |        |            |        |              | Ë.                     | - 27 |        |                            | ┍┛──┝     | ₽                                 |            |         |        |            |               |

|                                                                                               |                                             |                                                                                   |                                  |                     |                                          | 🖌 (1,<br>? (1,                              |        | 28         |        |              | ÷ 6-                   |      |        |                            |           |                                   |            |         |        |            |               |

| Des Ti ◀ ►                                                                                    | Total: 17 Fill                              |                                                                                   | RW_fails<br>RWEmpty              |                     |                                          | g (1,<br>✔ (1,                              | _      | ▲ 4<br>? 8 |        |              | ĕ.                     |      | nri II |                            |           |                                   |            |         |        |            |               |

| session_0                                                                                     |                                             | RWFull                                                                            |                                  |                     | <ul> <li>✓ (1,</li> <li>✓ (1,</li> </ul> |                                             | 28     |            |        | <b>▲</b> 4 - |                        |      |        | ی پر کا ا                  |           |                                   |            |         |        |            |               |

| - ar_cex :<br>- undetermined :<br>- unprocessed :<br>- error :<br>covers :<br>- unreachable : |                                             |                                                                                   | fifo_not_full                    |                     |                                          | <ul><li>✓ (1, 2)</li><li>✓ (1, 1)</li></ul> |        |            |        |              | 2 -                    |      |        | ЦЦЦ                        |           |                                   |            |         |        |            |               |

|                                                                                               |                                             | L                                                                                 | fifo full                        |                     |                                          | ? (1,                                       |        |            |        |              |                        | 1    |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               |                                             |                                                                                   | fifo empty                       |                     |                                          | <ul><li>✓ (1,</li></ul>                     |        |            |        |              |                        |      |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               |                                             |                                                                                   | Cover fifo not empty             |                     |                                          | <ul><li>✓ (1,</li></ul>                     |        |            |        |              | 0 -                    | -    |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               |                                             |                                                                                   |                                  |                     |                                          |                                             | _      |            |        | Ŭ            | 0                      |      |        |                            |           |                                   |            |         |        |            |               |

|                                                                                               | •                                           |                                                                                   |                                  | 1                   |                                          |                                             |        |            | F      |              |                        | 0.01 | 0.02   | 0.03                       |           | 0.04 0.05 0.06 0.07<br>• Time [s] |            |         |        |            |               |

|                                                                                               | Index Engine PID                            |                                                                                   |                                  | Host                |                                          |                                             | Stat   | Status     |        |              | Time                   |      |        | Memory (Resident) Progress |           |                                   |            | Proof 1 | of A   |            |               |

| - unprocessed<br>- error                                                                      |                                             | 0 PRE                                                                             |                                  | FID                 |                                          | nost                                        |        | Juan       | Status |              |                        | iine | 0.0 s  |                            |           | nory (Residenc) Progress          |            |         |        | <u> </u>   |               |

|                                                                                               | 0 Hp                                        |                                                                                   |                                  | snowy.cs.bris.ac.uk |                                          |                                             | Stop   | Stopped    |        |              | 0.1 s                  |      |        | 1                          | 10.99 MiB |                                   |            |         | - 11   |            |               |

| [ <embedded>] %</embedded>                                                                    |                                             | 0 Ht                                                                              |                                  |                     |                                          | snowy.cs.bris.ac.uk                         |        |            |        |              |                        |      | 0.1 s  |                            |           | 9.33 MiB                          |            |         |        |            | - 11          |

|                                                                                               |                                             | 0 N                                                                               |                                  |                     | sn                                       | snowy.cs.bris.ac.u                          |        | ac.uk      |        |              |                        |      |        |                            |           |                                   | 3.97 MiB   |         |        |            |               |

| Console Lint Messages Warnings                                                                |                                             | •                                                                                 | 0 B                              |                     | sn                                       | owy.c                                       | s.bris | ac.uk      | Stop   | ped          |                        |      | 1      | 0.                         | 1 s       |                                   | 7.19 Mil   | В       |        |            | <u>ا</u> لح , |

|                                                                                               |                                             | ProofGr                                                                           | rid Manager is                   | s Enabled           | _                                        |                                             |        |            | _      |              |                        |      |        |                            |           |                                   |            |         |        |            |               |

#### The demo session includes

- Automatic generation of basic properties using "Visualize":

- Basic functionality of the DUV

- Range checks of signals

#### Verification of SVA properties:

- "Empty and full are never asserted together."

- "After clear the FIFO is empty."

- "On empty after one write the FIFO is no longer empty."

#### Inspect and understand counterexamples:

- Debug several failed properties

- **Note:** Close link to coverage closure (by construction).

- Link from env\_constraints to simulation assertions.

#### Summary

#### **Functional Formal Verification**

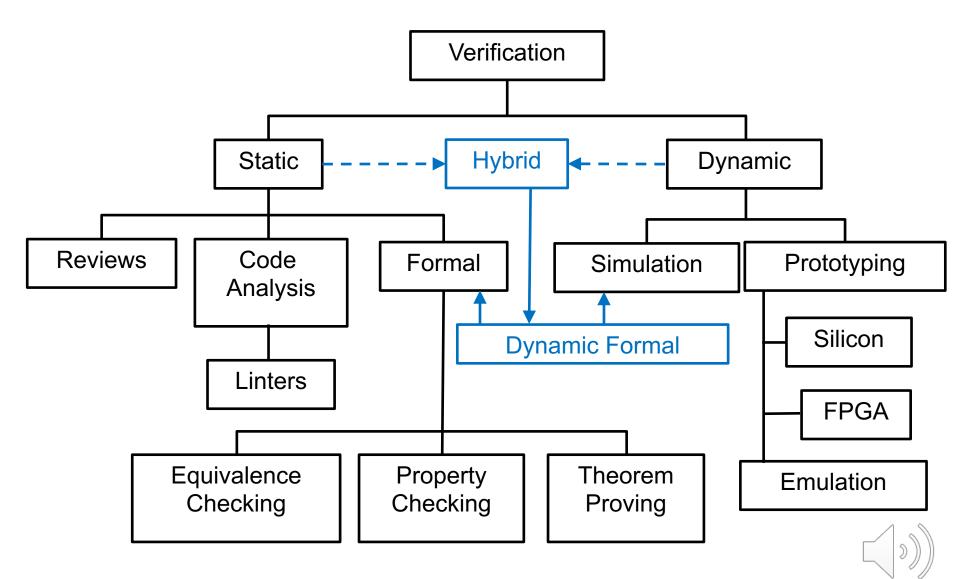

- Distinction between static and dynamic verification techniques

- Reconvergence model for formal verification

- What happens during formal verification

- Capacity limits and techniques to manage complexity

- Simulation vs. formal verification

- Outcomes of formal property checking

- Guidelines on writing properties

#### Conclusion

No single method is adequate to verify a whole design in practice.

- Carefully select the verification methods that maximize ROI for each level in the design hierarchy.

- Complement simulation with formal verification techniques to exploit the benefits and mitigate the limitations of each technique.